Guoli Li, Zizheng Fan, Nicolas André, Member, IEEE, Yongye Xu, Ying Xia, Benjamín Iñíguez, Fellow, IEEE, Lei Liao, Senior Member, IEEE, and Denis Flandre, Senior Member, IEEE

Non-Linear Output-Conductance Function for Robust Analysis of Two-Dimensional Transistors

IEEE Electron Device Letters, 42(1), pp.94-97

DOI: 10.1109/LED.2020.3042212

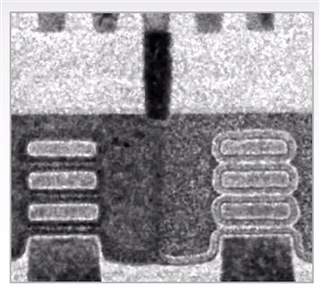

Abstract: In this work, we explore the outputconductance function (G-function) to interpret the device characteristics of two-dimensional (2D) semiconductor transistors. Based on analysis of the device output conductance, the carrier mobility, and the channel as well as contact resistance are extracted. Thereafter the currentvoltage (IV) characteristics of black phosphorous (BP) and MoS2 transistors from room to low temperature are modeled and compared to experiments. The G-function model proves its reliability and accuracy in parameter extraction and IV modeling of 2D transistors, regardless of the n- or p- type, the short- or long-channel and the Schottky or Ohmic contact. Moreover, this works shows its high potential in the device modeling and further circuit design of the 2D transistors, requiring only few parameters and simulating precise IV characteristics.

G-Function Model (for Linear and Non-Linear Cases), the Rch and Rc can be calculated for both the Ohmic and Schottky contacts in the 2D transistors:

Aknowlegement: This work was supported in part by the National Key Research and Development Program of China under Grant 2018YFA0703700; in part by the National Natural Science Foundation of China under Grant 61925403, Grant 61851403, and Grant 62004065; in part by the Hunan Natural Science Foundation under Grant 2020JJ5087; and in part by the Technology Program (Major Project) of Changsha under Grant kq1902042.