Dec 22, 2011

Trends confirming IEDM (by Jerzy Ruzyllo)

Dec 1, 2011

Synopsys to Acquire Magma Design Automation

MOUNTAIN VIEW, Calif., Nov. 30, 2011 /PRNewswire/ -- Synopsys, Inc. (Nasdaq:SNPS), a world leader in software and IP used in the design, verification and manufacture of electronic components and systems, has signed a definitive agreement to acquire Magma® Design Automation Inc. (Nasdaq:LAVA), a provider of chip design software headquartered in San Jose, California. Bringing together complementary technology, development and support capabilities will enable the combined company to more rapidly meet customer requirements linked to chip designs at both leading-edge and mature process nodes.

Under the terms of the merger agreement, Synopsys will acquire Magma for $7.35 per Magma share in cash, resulting in a transaction value of approximately $507 million net of cash and debt acquired. The boards of directors of both companies have unanimously approved the transaction.

The closing of the merger is subject to customary conditions, including approval by the stockholders of Magma as well as U.S. regulators. In the event the merger closes as expected in the second calendar quarter of 2012, Synopsys anticipates it to be modestly accretive to non-GAAP earnings per share in its fiscal 2012. Synopsys plans to fund the acquisition with a combination of cash and debt, with the specifics to be determined at the time of close.

"The dramatic rise in complexity of today's semiconductor designs for all process nodes requires an equally dramatic increase in designer productivity. Customers are either dealing with the very complex physics of 20-nanometer design or they are squeezing the last bit of performance and cost from designs at mature, high-value nodes. To achieve success, our customers are asking for more new EDA capabilities than ever before," said Aart de Geus, chairman and CEO at Synopsys. "This acquisition will enable Synopsys to accelerate the delivery of the technology our customers need to keep the overall cost of design in check."

Nov 20, 2011

[mos-ak] Final Program MOS-AK/GSA Washington DC Workshop on Dec.7 2011

====================================================

http://www.mos-ak.org/washington_dc/

* Free On-line Registration Form:

http://www.mos-ak.org/washington_dc/registration.php

* Venue:

The George Washington University Marvin Center

800 21st Street, Northwest, Suite 302

Washington, DC 20052

http://gwired.gwu.edu/marvincenter

* Agenda:

http://www.mos-ak.org/washington_dc/

With panel discussion:

Compact Model Verilog-A Standardization Panel

Geoffrey J. Coram, ADI (Moderator)

Marek Mierzwinski, Tiburon Design Automation (Introduction)

Panelists

Walter R. Curtice, WRC Consulting

Carlos Galup-Montoro UFSC, Brazil

Keith Green, TI, Compact Modeling Council

Benjamin Iniguez, URV, FP7 COMON Network

Local Organizing MOS-AK/GSA Committee:

======================================

Mona Zaghloul, GWU

Can E. Korman, GWU

John Suehle, NIST

Extended MOS-AK/GSA Committee:

==============================

Wladek Grabinski, GMC Suisse; MOS-AK/GSA Group Manager

Chelsea Boone, Director of Research GSA

* MOS-AK/GSA North America:

Chair: Pekka Ojala, Exar Corporation

Geoffrey Coram, Analog Devices

Jamal Deen, U.McMaster

Roberto Tinti, Agilent EEsof Division

* MOS-AK/GSA South America:

Chair: Gilson I Wirth; UFRGS; Brazil

Prof. Carlos Galup-Montoro, UFSC; Brazil

Sergio Bampi, UFRGS, Brazil

Antonio Cerdeira Altuzarra, Cinvestav - IPN, Mexico

* MOS-AK/GSA Europe:

Chair: Ehrenfried Seebacher, austriamicrosystems AG

Alexander Petr, XFab

Benjamin Iniguez, URV

James Victory, Sentinel-IC

* MOS-AK/GSA Asia/Pacific:

Chair: Goichi Yokomizo, STARC, Japan

Sadayuki Yoshitomi, Toshiba, Japan

A.B. Bhattacharyya, JIIT, India

Xing Zhou, NTU, Singapore

--

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To post to this group, send email to mos-ak@googlegroups.com.

To unsubscribe from this group, send email to mos-ak+unsubscribe@googlegroups.com.

For more options, visit this group at http://groups.google.com/group/mos-ak?hl=en.

Nov 11, 2011

[mos-ak] BSIM EKV Workshop at EPFL Lausanne on Dec. 15-16, 2011

The Nano-Tera Workshop on the Next Generation MOSFET Compact Models

15-16 December, 2011, EPFL

The BSIM group recently proposed BSIM6 as the new MOSFET compact model

to eventually replace BSIM3, BSIM4 and PSP for next generation bulk

CMOS processes. Trying to take advantage of the charge based features

of EKV, the BSIM research team from University of California,

Berkeley, led by Prof. Chenming Hu and the EKV modeling team at EPFL,

led by Prof. Christian Enz, decided to jointly develop the new BSIM6

compact model.

The BSIM EKV partnership has been officially announced by Profs. Hu

and Enz at the last ESSDERC-ESSIRC Conference during the MOS-AK

Workshop <http://mos-ak.org/helsinki/#BSIM-EKV>. The Nano-Tera

Workshop on the Next Generation MOSFET Compact Models will convene all

the BSIM and EKV researchers as well as the experts from the industry

to give an update on the latest status of BSIM6 and EKV (and

eventually other models as well) to the modeling and designer

community.

The detailed workshop program is available at: <http://ekv.epfl.ch/

workshop>

--

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To post to this group, send email to mos-ak@googlegroups.com.

To unsubscribe from this group, send email to mos-ak+unsubscribe@googlegroups.com.

For more options, visit this group at http://groups.google.com/group/mos-ak?hl=en.

Oct 7, 2011

Space and time combine to overpower the human brain

For example, Goldman said, a 1982 Intel 80286 was 28 times more powerful than computers on the Voyagers 1 and 2, launched in 1977. Sputnik computers were capable of only 2,000 instructions per second. And a 2010 Apple iPad is 689 times more powerful than the onboard computers on the Columbia space shuttle, first launched in 1981. [read more]

Oct 4, 2011

[mos-ak] C4P MOS-AK/GSA Workshop in Washington DC on Dec. 7 2011

-------------------------------------------------------

http://www.mos-ak.org/washington_dc/

-------------------------------------------------------

Together with the Organizing Committee and Extended MOS-AK/GSA TPC

Committee, we have pleasure to invite to the MOS-AK/GSA Workshop in

Washington DC on Dec. 7 2011

The MOS-AK/GSA Workshop is HiTech forum to discuss the frontiers of

the electron devices modeling with emphasis on simulation-aware

models. Original papers presenting new developments and advances in

the compact/spice modeling and its Verilog-A standardization are

solicited. The main topics of the workshop are: (but are not limited

to):

* Compact Modeling (CM) of the electron devices

* VHDL-AMS/Verilog-A for CM standardization

* New CM techniques and extraction software

* CM of passive, active, sensors and actuators

* Emerging devices, CMOS and SOI-based memory cells

* Microwave, RF device modeling, high voltage device modeling

* Transistor Level IC support

* Nanoscale CMOS devices and circuits

* Reliability and thermal management of electron devices

* Technology R&D, DFY, DFT and IC designs

* Foundry/Fabless interface strategies

The terms of participation:

-------------------------------------------------------

Authors are asked to submit a short (~200words) abstract using on-

line

submission form by OCT.30 http://www.mos-ak.org/washington_dc

Intending authors should also note the following deadlines:

* Announcement and Call for Papers - Oct 2011

* on-line abstract submission deadline - OCT.30, 2011

* Final Workshop Program - Nov. 2011

* MOS-AK/GSA Workshop - Dec. 7, 2011

-------------------------------------------------------

Further details and updates and on-line workshop registration:

http://www.mos-ak.org/washington_dc

Email contact: washington_dc@mos-ak.org

-------------------------------------------------------

--

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To post to this group, send email to mos-ak@googlegroups.com.

To unsubscribe from this group, send email to mos-ak+unsubscribe@googlegroups.com.

For more options, visit this group at http://groups.google.com/group/mos-ak?hl=en.

Oct 2, 2011

IBM Seeking:

[check: http://bit.ly/ny9DkU] #jobs #vermont

Sep 30, 2011

Nonvolatile Memory Standard CMOS Process

Sep 23, 2011

8th International Conference on Devices, Circuits and Systems (ICCDCS)

You can download the pdf version of the Call for Papers here.

[Internship] Modeling of GaN Power Transistors for IC Design

- Understanding of physical phenomena (electrical, thermal) in power HEMT transistors and analysis of existing models

- TCAD numerical simulations of devices.

- Compact modeling of transistors starting from previous studies on silicon carbide (SiC) transistors.

- Depending on availability, static and pulsed measurements on GaN transistors and extraction of model parameters.

Direction/Département/Service/Laboratoire CEA-LETI – DRT/DCOS/SCME/LSM

Postal address

CEA/GRENOBLE, MINATEC Campus,

17 rue des Martyrs 38054 Grenoble CEDEX 9

France

Technical Supervisor

Patrick MARTIN

Phone: 04 38 78 67 05

Sep 22, 2011

Sep 20, 2011

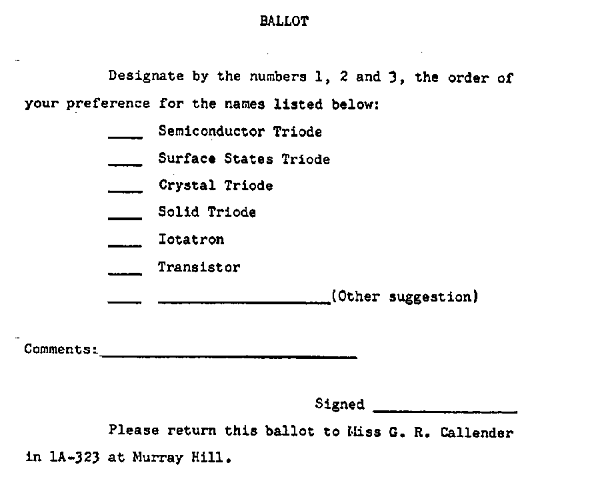

Digging into Technology's Past

Sep 13, 2011

FAST-SPICE BETA TESTERS WANTED

Sep 9, 2011

Sep 2, 2011

“The Ugly Duckling,” New Fairy Tales

Aug 31, 2011

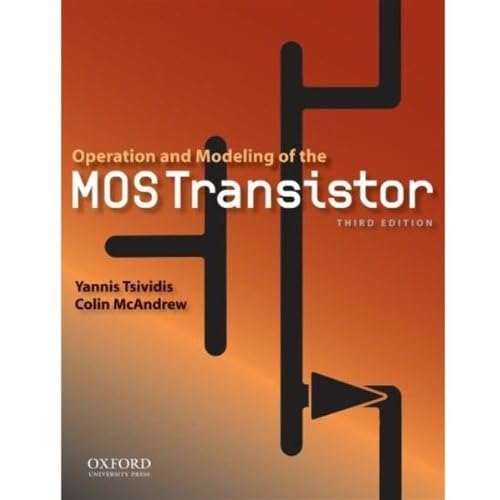

Operation and Modeling of the MOS Transistor

New to this edition:

- Energy bands and the energy barrier viewpoint are integrated into the discussion in a smooth, simple manner

- Expanded discussion of small-dimension effects, including velocity saturation, drain-induced barrier lowering, ballistic operation, polysilicon depletion, quantum effects, gate tunneling current, and gate-induced drain leakage

- Expanded discussion of small-signal modeling, including gate and substrate current modeling and flicker noise

- New chapter on substrate nonuniformity and structural effects, discussing transversal and lateral (halo) doping nonuniformity, stress and well proximity effects, and statistical variability

- A completely re-written chapter on modeling for circuit simulation, covering the considerations and pitfalls in the development of models for computer-aided design

- Extensively updated bibliography

- An accompanying website includes additional details not covered in the text, as well as model computer code

Jul 24, 2011

[mos-ak] Final Program MOS-AK/GSA ESSDERC/ESSCIRC Workshop in Helsinki on Sept.16 2011

program:

http://www.mos-ak.org/helsinki/

* Free On-line Registration Form:

http://essderc2011.org/registration_form.php

* Venue: Finlandia Hall in Helsinki, Finland

http://www.essderc2011.org/venue.php

* Agenda: Sept. 16, 2011: 8:30 - 16:30

http://www.mos-ak.org/helsinki/

With panel discussion: "40th Anniversary of SPICE"

(panelists alphabetic list)

Narain D. Arora, Siltera, USA

Christian Enz, EPFL, CH

Chenming Hu, UC Berkeley, USA

Willy Sansen, ESAT-MICAS, B (moderator)

Andrei Vladimirescu, BWRC, UC Berkeley, USA

Andreas Wild, ENIAC - JU, EU

--

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To post to this group, send email to mos-ak@googlegroups.com.

To unsubscribe from this group, send email to mos-ak+unsubscribe@googlegroups.com.

For more options, visit this group at http://groups.google.com/group/mos-ak?hl=en.

Jul 18, 2011

Post Doctoral Researcher / Research Engineer Position in Compact Modeling

- Research and development of new BSIM compact models

- Maintenance and support of BSIM MOSFET compact models (BSIM4, BSIMSOI and BSIM-MG)

- Interface with industry to understand requirements and issues with BSIM models and rectify them

- C & Verilog-A coding and testing/debugging of models

- Excellent semiconductor device physics and process technology knowledge

- Experience in computer programming (C and Verilog-A)

- Knowledge of basic analog and digital circuit operation

For more information, please visit:

BSIM Group and Device Group

Jun 29, 2011

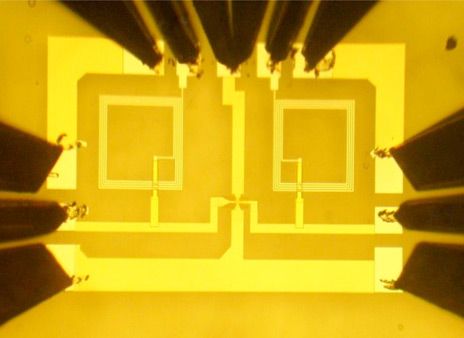

Arrays of indefinitely long uniform nanowires and nanotubes

Arrays of indefinitely long uniform nanowires and nanotubes

- Mecit Yaman,

- Tural Khudiyev,

- Erol Ozgur,

- Mehmet Kanik,

- Ozan Aktas,

- Ekin O. Ozgur,

- Hakan Deniz,

- Enes Korkut

- & Mehmet Bayindir

- Nature Materials 10, 494–501 (2011)

- doi:10.1038/nmat3038

http://www.nature.com/nmat/journal/v10/n7/full/nmat3038.html

It's frankly nice.... see one of their pictures (hope they don't get too upset!):

Jun 23, 2011

SISPAD 2011 Companion Workshops

- Compact Modeling

- Organizer: Sadayuki Yoshitomi, Toshiba Corporation

- Power Devices

- Organizer: Ichiro Omura, Kyusyu Institute of Technology

SuVolta creates new transistor option for 20 nm

Jun 22, 2011

Job offers at RF Micro Devices (RFMD)

Tracking Code Job Title Location Date Posted

| 12134 | Senior Modeling Engineer | Greensboro, NC, US | 6/7/2011 |

| 12117 | Sr. TCAD Modeling Engineer | Greensboro, NC, US | 5/26/2011 |

| 12116 | Sr. Modeling Engineer | Greensboro, NC, US | 5/24/2011 |

Note that this is only a re-diffusion of some information we've got, and that we're not related to them in any way!

Jun 17, 2011

Get your own version of Myfab LIMS

IMEC benchmarks FinFET superiority

By Peter Clarke, EE Times -- EDN, June 16, 2011

The benchmark circuits were six-transistor SRAM cells and SRAM arrays and IMEC has concluded that the FinFET outperforms planar CMOS in variability-aware and technology-aware comparison of SRAM product yield.

Both FinFET on bulk and FinFET on silicon-on-insulaor (SOIFF) technologies come out superior to the planar technology for medium- to large-sized SRAM arrays resulting in higher yields, IMEC said, although it did not disclose the process geometry at which the tests were done. It is likely to have been at around 28 to 22 nm.

As the dimensions of devices scale down, the variations in the electrical parameters of CMOS transistors steadily increase. This is due to random fluctuations in the density of the dopants in the channel, source, and drain. So, two closely placed transistors that are supposedly identical can show a widely different behavior. This makes the design of SRAM memory cells less predictable and controllable for every new technology node.

Because of this scaling 6T planar SRAMs below 22 nm remains challenging, IMEC said. FinFET devices show a lower leakage and variability and it is possible to design more compact cells.

Both FinFET technologies come out as superior to planar for SRAM arrays of greater than 128 kbytes. They are less sensitive to mismatches, thus allowing a more aggressive scaling of the power supply and a lower VCC than planar arrays. For undoped silicon-on-insulator FinFETs (SOIFF), the power supply can be lowered by an additional 200-mV compared to planar. As a sample result: undoped SOIFF FinFET allow for a 95% yield at 0.7-V in 32-Mbit SRAM arrays, moving to Gbit arrays for higher voltages.

Jun 15, 2011

A new birth in the IEEE journals world...

Let's welcome them!

They are starting with some interesting papers on low-power and analog design with nanometer-scale variations.... Let's hope they go on...

IEEE Journal of Emerging and Selected Topics in Circuits and Systems (JETCAS) We are honored to welcome readers and authors to the inaugural issue of the IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS for short), which is sponsored by the IEEE Circuits and Systems Society (CAS-S.) The journal, which is freely accessible on-line to all CAS-S members, aims to build a platform for the broad and timely dissemination of key innovative results and findings in rapidly-growing and/or emerging topic areas within the scope of the IEEE Circuits and Systems Society. Such potentially interdisciplinary emerging topics will be selected as long as, first, they are clearly situated at the forefront of current scientific and technological developments and, second, they are expected to grow over time in scientific and professional importance and, therefore, in the number of active practitioners. From this point of view, JETCAS is expected to create new communities interested in the long-term development of the most promising subjects presented in the journal. The editorial strategy followed by JETCAS will be the publication of Special Issues on the selected topics. These issues will include research contributions from leading experts and presentations geared towards a wide audience of scientists and pra MASSOUD PEDRAM, Editor-in-Chief (EiC) MANUEL DELGADO-RESTITUTO, Deputy EiC ENRICO MACII, 2010-2011 VP Publications, IEEE CAS-S GIANLUCA SETTI, 2010 President, IEEE CAS-S Volume 1, Issue 1 - Inaugural Edition http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=5503868 Pedram, M.; Delgado-Restituto, M.; Macii, E.; Setti, G., Inaugural Editorial http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5765455 ----------------------------------------------------------------------------------------------------- Variation-Aware Design for Nanoscale VLSI Circuits and Systems The focus of this issue is on the challenges faced in designing digital and analog circuits in nanoscale technologies, where variations due to process, environmental, and aging variations are substantial. The root causes of these effects can generally be traced to scaling: with the drive towards even greater miniaturization, these problems become even more acute and it is imperative that they be addressed. The solutions involve the invention of improved design techniques, better design automation, and closer interactions between the phenomenological root causes and the designer. The six papers in this issue attempt to provide a view of the landscape, reflecting the current state of the art and future directions. Sapatnekar, S. S., Guest Editorial http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5762378 ------------------------------------------------------------------------------------------------------------------ Sapatnekar, S. S., Overcoming Variations in Nanometer-Scale Technologies http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5762377 Nanometer-scale circuits are fundamentally different from those built in their predecessor technologies in that they are subject to a wide range of new effects that induce on-chip variations. These include effects associated with printing finer geometry features, increased atomic-scale effects, and increased on-chip power densities, and are manifested as variations in process and environmental parameters and as circuit aging effects. The impact of such variations on key circuit performance metrics is quite significant, resulting in parametric variations in the timing and power, and potentially catastrophic failure due to reliability and aging effects. Such problems have led to a revolution in the way that chips are designed in the presence of such uncertainties, both in terms of performance analysis and optimization. This paper presents an overview of the root causes of these variations and approaches for overcoming their effects. ----------------------------------------------------------------------------------------------------------------- Karakonstantis, G.; Chatterjee, A.; Roy, K., Containing the Nanometer "Pandora-Box": Cross-Layer Design Techniques for Variation Aware Low Power Systems http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5766061 The demand for richer multimedia services, multifunctional portable devices and high data rates can only been visioned due to the improvement in semiconductor technology. Unfortunately, sub-90 nm process nodes uncover the nanometer Pandora-box exposing the barriers of technology scaling-parameter variations, that threaten the correct operation of circuits, and increased energy consumption, that limits the operational lifetime of today's systems. The contradictory design requirements for low-power and system robustness, is one of the most challenging design problems of today. The design efforts are further complicated due to the heterogeneous types of designs (logic, memory, mixed-signal) that are included in today's complex systems and are characterized by different design requirements. This paper presents an overview of techniques at various levels of design abstraction that lead to low power and variation aware logic, memory and mixed-signal circuits and can potentially assist in meeting the strict power b ----------------------------------------------------------------------------------------------------------------- Mitra, S.; Brelsford, K.; Kim, Y. M.; Lee, H.-H. K.; Li, Y., Robust System Design to Overcome CMOS Reliability Challenges http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5751208 Today's mainstream electronic systems typically assume that transistors and interconnects operate correctly over their useful lifetime. With enormous complexity and significantly increased vulnerability to failures compared to the past, future system designs cannot rely on such assumptions. For coming generations of silicon technologies, several causes of hardware reliability failures, largely benign in the past, are becoming significant at the system level. Robust system design is essential to ensure that future systems perform correctly despite rising complexity and increasing disturbances. This paper describes three techniques that can enable a sea change in robust system design through cost-effective tolerance and prediction of failures in hardware during system operation: 1) efficient soft error resilience; 2) circuit failure prediction; and 3) effective on-line self-test and diagnostics. The need for global optimization across multiple abstraction layers is also demonstrated. ----------------------------------------------------------------------------------------------------------------- Seok, M.; Chen, G.; Hanson, S.; Wieckowski, M.; Blaauw, D.; Sylvester, D., CAS-FEST 2010: Mitigating Variability in Near-Threshold Computing http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5762379 Near threshold computing has recently gained significant interest due to its potential to address the prohibitive increase of power consumption in a wide spectrum of modern VLSI circuits. This tutorial paper starts by reviewing the benefits and challenges of near threshold computing. We focus on the challenge of variability and discuss circuit and architecture solutions tailored to three different circuit fabrics: logic, memory, and clock distribution. Soft-edge clocking, body-biasing, mismatch-tolerant memories, asynchronous operation and low-skew clock networks are presented to mitigate variability in the near threshold ${V} _{rm DD}$ regime. ----------------------------------------------------------------------------------------------------------------- Maricau, E.; Gielen, G., Computer-Aided Analog Circuit Design for Reliability in Nanometer CMOS http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5762376 Integrated analog circuit design in nanometer CMOS technologies brings forth new and significant reliability challenges. Ever-increasing process variability effects and transistor wear-out phenomena such as BTI, hot carrier degradation and dielectric breakdown force designers to use large design margins and to increase the uncertainty on the circuit lifetime. To help designers to tackle these problems at design time (i.e., Design For Reliability, or DFR), accurate transistor aging models, efficient circuit reliability analysis methods and novel design techniques are needed. The paper overviews the current state of the art in DFR for analog circuits. The most important unreliability effects in nanometer CMOS technologies are reviewed and transistor aging models, intended for accurate circuit simulation, are described. Also, efficient methods for circuit reliability simulation and analysis are discussed. These methods can help designers to analyze their circuits and to identify weak spots. Finally, cost-effect ----------------------------------------------------------------------------------------------------------------- Zhang, X.; Mukadam, M. Y.; Mukhopadhyay, I.; Apsel, A. B., Process Compensation Loops for High Speed Ring Oscillators in Sub-Micron CMOS http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5756255 In this paper, we present two implementations of a closed-loop process compensation scheme for high speed ring oscillators-the comparator based and the switched capacitor based loops. We provide detailed discussion of the frequency accuracy, loop stability, and implementation cost for each design. More than 150 test chips from multiple wafer-runs in a 90 nm CMOS process verify that frequency accuracy of better than 2.6% can be achieved with the application of the proposed compensation loop. Moreover, by leveraging a low variation addition-based current source, we have demonstrated a fully-integrated 2.15 GHz ring oscillator with less than 4.6% frequency variation without external references or post fabrication calibration, which is 3.8 $times$ improvement in frequency accuracy over the baseline case. The same compensation scheme can also alleviate frequency drift caused by temperature. JETCAS is published quarterly and solicits, with particular emphasis on emerging areas, special issues on topics that cover the entire scope of the IEEE Circuits and Systems (CAS) Society, namely the theory, analysis, modeling, design, automation, and implementation of electronic circuits and systems, spanning theoretical foundations, applications, and architectures for signal and information processing.

Jun 13, 2011

First Graphene Integrated Circuit

IBM researchers have built the first IC based on a graphene transistor. It is another step toward overcoming the limits of silicon and a potential path to flexible electronics [read more at spectrum.ieee.org]

Jun 10, 2011

Alternative semiconductor fabrication methods enable inexpensive, conformable consumer devices - Solid State Technology

Emerging technology and a developing infrastructure for printed electronics is enabling circuitry that is flexible, conformable, and inexpensive to mass-produce. FlexTech Alliance has identified, funded, and directed advanced development in the flexible and printed electronics infrastructure, paving the way for the practical manufacture of a variety of low-cost applications such as electronic packaging, ID tags, and wide-area lighting panels.

Printed electronics include a set of consumer markets where printed logic and memory will be required. The size and cost of fully printed systems is set to challenge silicon-based technologies in ultra-high-volume distributed applications. To address this issue, Norwegian firm ThinFilm Electronics produces rewritable memory tags manufactured using full roll-to-roll (R2R) printing. Printed non-volatile RAM (NVRAM), when combined with printed transistor elements, serves as the basis of a new generation of cheap, disposable, and highly ubiquitous electronic devices. The company is working with major toy and game companies and has established high-volume manufacturing to deliver millions of tags per month.

In other commercial development, a new method for fabricating printed semiconductors, developed by NthDegree Technologies, allows a standard high-speed printing press to print conductive ink on to paper, plastic, or other substrate materials. Printed semiconductors made with these inks reduce the cost of producing semiconductor-based devices while creating innovative conformable products. Wide-area lighting is currently being produced with this technology by means of a light-emitting diode (LED) "ink". This LED ink is being used to print area lighting that is converted into a flat panel to replace fluorescent tube fixtures.

These latest developments in printed electronics materials, tools and processes, including LED lighting and printed memory, will be discussed and demonstrated at the Extreme Electronics TechXpot session "Printed electronics: Beyond R&D to real-deal technologies," presented by the FlexTech Alliance at SEMICON West, July 14, 2011. For more information about FlexTech Alliance visit www.flextech.org.

Freescale's Su calls for improved EDA tools

As more embedded devices are being connected to the "Internet of things" the design methodologies used in IC designs need to change accordingly for faster chip turnarounds.

Lisa Su, VP and general manager of Freescale"Some 7 billion devices will be connected to the Internet in this era from 2006 to 2020," said Lisa Su, vice president and general manager of Freescale Semiconductor Inc's networking and multimedia group. "And mobile traffic is doubling every year through 2015."

Su delivered the Tuesday (June 7) keynote here at the Design Automation Conference, whose organizers have placed embedded systems and software squarely in the apex of DAC with dedicated exhibit areas on the show floor.

While only 15 exhibitors specifically identified themselves as embedded hardware/software providers out of a total of 200, the technical program was loaded with embedded presentations and Su's keynote was clearly aimed at showing that at least Freescale understands that it is operating in a new space for them, the embedded world.

"The embedded era is defined by standards-based hardware and software, is open source, and aimed numerous markets, including health, safety, energy, transportation, communications, entertainment, automation, and, of course, cloud computing," said Su.

Su quoted statistics that the monthly mobile traffic will increase tenfold from today's 0.6 exabytes to 6.3 exabytes by 2015. "The resultant heterogeneous networks, together with the increasing needs of the ‘connected' car, offer many opportunities to semiconductor companies like us," said Su.

The many-core paradigm of the expected SOC technology transition poses a few challenges, according to Su.

Among these are scalability as the number of cores per processor generation will double. Also there will be system tradeoffs to consider between cores versus using hardware acceleration, as well cluster optimization among cores, caches, local vs. global resource sharing. And an increasing amount of high-speed mixed-signal I/O will place strain on expected quality of service metrics.

read more...

Jun 8, 2011

Postdoc Position in Thin Films (Thun, CH)

Submit your application online and upload all documents through this webpage by June 30, 2011:

http://internet1.refline.ch/673276/0190/++publications++/1/index.html

Additional information can be obtained from the EMPA website and by contacting Dr. Johann Michler.

IEDM'2011 Abstract Submission Site is Now Open (Deadline: June 24, 2011)

IEDM Abstract Submission Site is Now Open - Abstract Submission Deadline: June 24, 2011 2011 IEEE International Electron Devices Meeting The Annual Technical Meeting of the Electron Devices Society will be held at the Washington Hilton, Washington, DC USA - December 5-7, 2011 To view the IEDM Call for Papers and instructions for submitting an abstract to the conference, visit: http://www.ieee-iedm.org IEEE International Electron Devices Meeting (IEDM) is the world’s pre-eminent forum for reporting technological breakthroughs in the areas of semiconductor and electronic device technology, design, manufacturing, physics, and modeling. IEDM is the flagship conference for nanometer-scale CMOS transistor technology, advanced memory, displays, sensors, MEMS devices, novel quantum and nano-scale devices and phenomenology, optoelectronics, devices for power and energy harvesting, high-speed devices, as well as process technology and device modeling and simulation. Starting this year (2011) there is an increased emphasis on circuit and device interaction. With ever increasing transistor count, nanometer design rules and layout restrictions, circuit-device interaction is becoming critical to providing viable technology solutions. This new emphasis includes technology/circuit co-optimization, power/performance/area analyses, design for manufacturing and process control, as well as CMOS platform technology and scaling. INCREASED PARTICIPATION IN THE FOLLOWING AREAS IS SOUGHT: * Circuit-device interaction * Energy harvesting * Biomedical devices * Power devices Information about IEDM can be found at: http://www.ieee-iedm.org Twitter: http://twitter.com/ieee_iedm Facebook: http://www.facebook.com/pages/IEDM/131119756449 MEETING HIGHLIGHTS * New subcommittees (Circuit-Device Interaction and Nano Device Technology) * New for 2011: 90 Minute Tutorial Sessions on Emerging Topics, Saturday afternoon, December 3 * Three plenary presentations by prominent experts * Invited papers on all aspects of advanced devices and technologies. * An Emerging Technology session. * Two evening Panel discussions. * Presentation of IEEE/EDS awards. * IEDM Luncheon presentation will be held on Tuesday, December 6. * Two short courses will be held on Sunday, December 4. Further Information - All questions or inquiries for further information regarding this meeting should be directed to the Conference Office at: 19803 Laurel Valley Place Montgomery Village, MD 20886 USA Tel: 301-527-0900, ext. 2 Email: iedm@his.com Local European Contact Stefan De Gendt, IMEC, Belgium Local Asian Contact Norikatsu Takaura, LEAP, Japan 2011 Conference Chair Kazunari Ishimaru, Toshiba, Japan Technical Program Chair Veena Misra, North Carolina State University, USA If you know of any colleagues who may have a paper to contribute and have not received this notice, please bring it to their attention.

Jun 3, 2011

Course on Statistical CMOS Variability and Reliability, San Jose CA, June 13th and 14th

The course topics include, Variability classification,Sources of statistical variability, Simulation of statistical variability, Variability trends in conventional and novel MOSFETs, Random telegraph noise statistics, Statistical aspects of reliability, Statistical compact model strategies and Statistical circuit simulation. At this event there will also be a special lecture on Variability in FinFET devices.

For more information please visit: http://www.goldstandardsimulations.com/courses/ or get in touch with them at courses(at)goldstandardsimulations.com.

Jun 2, 2011

Papers in Solid-State Electronics Volume 62, Issue 1, (August 2011)

Pages 31-39

Darsen D. Lu, Mohan V. Dunga, Chung-Hsun Lin, Ali M. Niknejad, Chenming Hu

Research highlights

► A computationally efficient approximation for surface potential in FDSOI MOSFETs is developed. ► I–V and C–V models for FDSOI MOSFETs are derived without making the charge sheet approximation. ► The core model and non-ideal effect expressions are implemented in Verilog-A language. ► The model is symmetric with respect to Vds = 0 and continuous in all regions of operation.An effective thermal circuit model for electro-thermal simulation of SOI analog circuits Original Research Article

Pages 48-61

Ming-C. Cheng, Kun Zhang

Highlights

► A thermal circuit model is developed for SOI analog circuits. ► The model integrates a device thermal circuit with interconnect thermal networks. ► The device thermal circuit accounts for non-isothermal effects in SOI devices. ► Thermal networks for cross-coupled and parallel coupled wires are developed. ► The model is coupled with BSIMSOI for electro-thermal simulation of SOI circuits.MOSFET modeling for design of ultra-high performance infrared CMOS imagers working at cryogenic temperatures: Case of an analog/digital 0.18 μm CMOS process Original Research Article

Pages 115-122

P. Martin, A.S. Royet, F. Guellec, G. Ghibaudo

Research highlights

► Specific physical effects are observed in a cooled (77–200 K) 0.18 μm CMOS process. ► These effects are described and modeled for design of cryogenic IR CMOS imagers. ► Data on low frequency noise and transistor matching in MOSFET are also presented.Physics-based compact model for ultra-scaled FinFETs Original Research Article

Pages 165-173

Ashkhen Yesayan, Fabien Prégaldiny, Nicolas Chevillon, Christophe Lallement, Jean-Michel Sallese

Highlights

► We propose a physical and explicit compact model for lightly doped FinFETs. ► This design-oriented model is valid for a large range of silicon Fin widths/lengths. ► It describes well the drain current, small signal parameters and capacitances. ► It takes into account all short-channel effects and quantum mechanical effects. ► This compact model needs a very few number of electrical parameters (4).Three-dimensional analytic modelling of front and back gate threshold voltages for small geometry fully depleted SOI MOSFET’s Original Research Article

Pages 174-184

Krishna Meel, R. Gopal, Deepak Bhatnagar

Highlights

► New 3-D front (back) gate threshold voltage models of FD-SOI MOSFETs are reported. ► Models solve 3-D Poisson’s equation using Green’s function as a tool. ► 3-D threshold voltage models include side wall, source/drain and back gate effects. ► Front and back gate charge coupling is incorporated in both the threshold voltages. ► Compact models of threshold voltages are amenable to circuit CAD tool.Mobility analysis of surface roughness scattering in FinFET devices Original Research Article

Pages 195-201

Jae Woo Lee, Doyoung Jang, Mireille Mouis, Gyu Tae Kim, Thomas Chiarella, Thomas Hoffmann, Gérard Ghibaudo

Highlights

► Mobility analysis of the surface roughness scattering along the different interfaces of FinFET devices. ► The sidewall and top surface drain current components were estimated from the total drain currents of different fin width conditions. ► The contribution of the surface roughness scattering was analysed and that on sidewalls was about three times stronger than on top surface for n-channel FinFETs.Jun 1, 2011

[mos-ak] C4P MOS-AK/GSA ESSDERC/ESSCIRC Workshop in Helsinki on Sept.16 2011

http://www.mos-ak.org/helsinki/

Together with the Organizing Committee and Extended MOS-AK/GSA TPC

Committee, we have pleasure to invite to the MOS-AK/GSA Workshop in

Helsinki on Sept.16 2011 with special panel: 40th Anniversary of SPICE

(panelists tentative alphabetic list):

* Narain D. Arora, Siltera, USA

* Christian Enz, CSEM, CH

* Andrei Vladimirescu, EECS, Berkeley

* Andreas Wild, ENIAC - JU, EU

and MOS-AK/GSA Transistor Level IC Design Challenge Opening

The MOS-AK/GSA Workshop is HiTech forum to discuss the frontiers of

the electron devices modeling with emphasis on simulation-aware

models. Original papers presenting new developments and advances in

the compact/spice modeling and its Verilog-A standardization are

solicited. The main topics of the workshop are: (but are not limited

to):

* Compact Modeling (CM) of the electron devices

* VHDL-AMS/Verilog-A for CM standardization

* New CM techniques and extraction software

* CM of passive, active, sensors and actuators

* Emerging devices, CMOS and SOI-based memory cells

* Microwave, RF device modeling, high voltage device modeling

* Transistor Level IC support

* Nanoscale CMOS devices and circuits

* Reliability and thermal management of electron devices

* Technology R&D, DFY, DFT and IC designs

* Foundry/Fabless interface strategies

The terms of participation:

Authors are asked to submit a short (~200words) abstract using on-line

submission form by JUNE 30 http://www.mos-ak.org/helsinki/abstracts.php

Intending authors should also note the following deadlines:

* Announcement and Call for Papers - May 2011

* on-line abstract submission deadline - June 30, 2011

* Final Workshop Program - August 2011

* MOS-AK/GSA Workshop - Sept. 16, 2011

On-line workshop registration: http://www.essderc2011.org/registration.php

Further details and updates: http://www.mos-ak.org/helsinki

Email contact: helsinki@mos-ak.org

--

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To post to this group, send email to mos-ak@googlegroups.com.

To unsubscribe from this group, send email to mos-ak+unsubscribe@googlegroups.com.

For more options, visit this group at http://groups.google.com/group/mos-ak?hl=en.

May 25, 2011

Papers for curious people... (may 25th 2011)

CMOS Silicon Physical Unclonable Functions Based on Intrinsic Process Variability

Stanzione, S. Puntin, D. Iannaccone, G.Page(s): 1456 - 1463

Digital Object Identifier : 10.1109/JSSC.2011.2120650

A Supply-Rail-Coupled eTextiles Transceiver for Body-Area Networks

Mercier, P. P. Chandrakasan, A. P.Page(s): 1284 - 1295

Digital Object Identifier : 10.1109/JSSC.2011.2120690

Statistical Modeling and Simulation of Threshold Variation Under Random Dopant Fluctuations and Line-Edge Roughness

Ye, Y. Liu, F. Chen, M. Nassif, S. Cao, Y.Page(s): 987 - 996

Digital Object Identifier : 10.1109/TVLSI.2010.2043694

On Functional Broadside Tests With Functional Propagation Conditions

Pomeranz, I. Reddy, S. M.Page(s): 1094 - 1098

Digital Object Identifier : 10.1109/TVLSI.2010.2043695

Broadside and Functional Broadside Tests for Partial-Scan Circuits

Pomeranz, I. Reddy, S. M.Page(s): 1104 - 1108

Digital Object Identifier : 10.1109/TVLSI.2010.2044049

Papers in IEEE TED, vol 58, issue 6 (june 2011)

An Efficient Robust Algorithm for the Surface-Potential Calculation of Independent DG MOSFET

Jandhyala, S. Mahapatra, S.Page(s): 1663 - 1671

Digital Object Identifier : 10.1109/TED.2011.2131654

Statistical Model of Line-Edge and Line-Width Roughness for Device Variability Analysis

Hiraiwa, A. Nishida, A. Mogami, T.Page(s): 1672 - 1680

Digital Object Identifier : 10.1109/TED.2011.2131144

A Physics-Based Analytical Compact Model for the Drift Region of the HV-MOSFET

Bazigos, A. Krummenacher, F. Sallese, J.-M. Bucher, M. Seebacher, E. Posch, W. Moln??r, K. Tang, M.Page(s): 1710 - 1721

Digital Object Identifier : 10.1109/TED.2011.2119487

Papers in IEEE EDL, vol 32, issue 6 (may 2011)

Modeling of Current-Return-Path Effect on Single-Ended Inductor in Millimeter-Wave Regime

Wang, H. Zhang, L. Yang, D. Zeng, D. Wang, Y. Yu, Z.Page(s): 737 - 739

Digital Object Identifier : 10.1109/LED.2011.2136312

Simple Analytical Bulk Current Model for Long-Channel Double-Gate Junctionless Transistors

Duarte, J. P. Choi, S.-J. Moon, D.-I. Choi, Y.-K.Page(s): 704 - 706

Digital Object Identifier : 10.1109/LED.2011.2127441

Modeling and Separate Extraction of Gate-Bias- and Channel-Length-Dependent Intrinsic and Extrinsic Source–Drain Resistances in MOSFETs

Bae, H. Jang, J. Shin, J. S. Yun, D. Lee, J. Kim, T. W. Kim, D. H. Kim, D. M.Page(s): 722 - 724

Digital Object Identifier : 10.1109/LED.2011.2131116

Extraction of Separated Source and Drain Resistances in Amorphous Indium–Gallium–Zinc Oxide TFTs Through  –

–  Characterization

Characterization

Bae, H. Kim, S. Bae, M. Shin, J. S. Kong, D. Jung, H. Jang, J. Lee, J. Kim, D. H. Kim, D. M. Page(s): 761 - 763

Digital Object Identifier : 10.1109/LED.2011.2127438

Mechanism Analysis of Off-Leakage Current in an LDD Poly-Si TFT Using Activation Energy

Nakashima, A. Kimura, M.Page(s): 764 - 766

Digital Object Identifier : 10.1109/LED.2011.2132112

Evidence of a Novel Source of Random Telegraph Signal in CMOS Image Sensors

Goiffon, V. Magnan, P. Martin-Gonthier, P. Virmontois, C. Gaillardin, M.Page(s): 773 - 775

Digital Object Identifier : 10.1109/LED.2011.2125940

Temperature Dependence of the Threshold Voltage Shift Induced by Carrier Injection in Integrated STI-Based LDMOS Transistors

Poli, S. Reggiani, S. Denison, M. Gnani, E. Gnudi, A. Baccarani, G. Pendharkar, S. Wise, R.Page(s): 791 - 793

Digital Object Identifier : 10.1109/LED.2011.2135835

RF Model and Verification of Through-Silicon Vias in Fully Integrated SiGe Power Amplifier

Liao, H.-Y. Chiou, H.-K.Page(s): 809 - 811

Digital Object Identifier : 10.1109/LED.2011.2136313

Channel-Length-Dependent Transport Behaviors of Graphene Field-Effect Transistors

Han, S.-J. Chen, Z. Bol, A. A. Sun, Y.Page(s): 812 - 814

Digital Object Identifier : 10.1109/LED.2011.2131113

May 20, 2011

Marie Curie PhD position in Catania, Italy

it is a pleasure to inform you that a Marie Curie Early Stage Researcher

position is available at the Institute for Microelectronics and

Microsystem of the National Research Council of Italy (IMM-CNR) in

Catania.

The position is on the topic "Physical issues at interfaces and

nanoscale in advanced SiC devices", and it is open in the framework of

the FP7 Marie Curie ITN - NetFISiC (Training NETwork on Functional

Interfaces for SiC).

You can find more information on the position in the following link:

http://ec.europa.eu/euraxess/index.cfm/jobs/jobDetails/33681023

Would you please inform all the potential applicants for this position

(graduated students in Physics, Engineering or Material Science ) about

this good opportunity.

Should you need more information, contact:

Fabrizio Roccaforte

CNR-IMM

Strada VIII n.5, Zona Industriale

I-95121 Catania

Italy

tel. +39-0955968226

fax. +39-0955968312

e-mail: fabrizio.roccaforte@imm.cnr.it

May 17, 2011

International Journal of Numerical Modelling: Electronic Networks, Devices and Fields, MAY 2011

A physically based, accurate compact model of direct tunneling gate current considering quantum mechanical effects in nanoscale metal-oxide-semiconductor field-effect transistors

- M. A. Karim1,2,*,

- Q. D. M. Khosru1

International Journal of Numerical Modelling: Electronic Networks, Devices and Fields

May 12, 2011

Open Ph D scholarship in semiconductor device modeling

We offer one scholarship for a Ph D student position in the Department of Electronic Engineering in the Universitat Rovira i Virgili (URV), in Tarragona, Spain.

The duration of the grant will be for four years. The monthly salary will be about 1000 Euro/month. The position will start in September 2011.

The candidate should have a Bachelor or Master degree in Electrical Engineering, Electronic Engineering, Telecommunication Engineering or Physics. A good background in Semiconductor Physics, Semiconductor Devices, or Integrated Circuit Design will be highly appreciated.

The work to be done by the candidate will be focused on the development of new techniques of characterization and modeling of novel advanced semiconductor devices, in particular nanoscale MOSFETs. It will be related to several European projects in which the hosting group participates, in particular the COmpact MOdelling Netwok (COMON), that is led by the hosting group (the so-called NEPHOS group) and the SQWIRE (Silicon Quantum WIREs) project, about junctionless nanowires.

The NEPHOS group at URV is one of the most powerful teams in Europe in the area of compact modeling of semiconductor devices.

Required documents for applicants

Applicants are required to send to the address specified below the following documents (in English or Spanish):

1) a full Curriculum Vitae (as complete as possible) with passport number

2) Copy of their diploma

3) copy of their passport

4) Academic certificate including their marks (it is important that the number of hours or credits of each subject appears). It is also very important that the document specifies what is the minimum mark for passing a given subject and what is the maximum mark that can be awarded.

Candidates are requested to send their documents by e-mail to:

Prof. Benjamin Iñiguez

Department of Electronic, Electrical and Automatic Control Engineering

Universitat Rovira i Virgili (URV)

Avinguda Països Catalans, 26

43007 Tarragona (Spain)

Email: benjamin.iniguez@gmail.com

Tel: +34977558521 Fax:+34977559610

Deadline: May 31 2011

You can contact Prof. Benjamin Iñiguez (Benjamin.Iniguez@gmail.com) for more information

Tarragona is a medium city (100000 inhabitants) with a Mediterranean climate and many recreation opportunities (nice beaches, theme parks, nature preserves, mountain hiking, touristic resorts and facilities). It is located 100 km Southwest of Barcelona, and it is very well connected by train, bus, highways and even low cost flights from its own airport. Additional information about the University and the department can be found at: www.urv.cat and sauron.etse.urv.es