plus additional technical talks

Sep 29, 2023

[workshop] QC:DCEP 2023

plus additional technical talks

Sep 28, 2023

[C4P] 36th ICMTS 2024

- Design

- Methodologies, Verification

- Within-die circuits for process characterization/monitoring

- Design enablement – Characterization and validation of digital and analog libraries

- Devices and Circuit Modelling

- Measurement techniques

- DC, AC and RF measurements: setup, test and analysis

- Reliability test - including thermal stability, failure analysis etc.

- Statistical analysis, variability, throughput increase, smart test strategies

- Use of machine learning and AI in analysis of data sets - parameter extraction etc.

- Wafer probing, within-die measurements, in-line metrology

- Throughput, testing strategies, yield enhancement and process control tests

- Applications

- Emerging memory technologies (single cell, arrays, and application in neural networks)

- Emerging transistor technologies for digital/analog/power applications

- Photonic devices - silicon integration, new displays (OLED, μ-displays)

- Flexible electronics and sensors (organic and inorganic materials)

- M(N)EMS, actuators, sensors, PV cells and other emerging devices

The abstract submission deadline is October 27th, 2023.

Abstracts can be submitted via the ICMTS 2024 website www.icmts.net using the “Abstract Submission” link on the front page. Notice of paper acceptance will be sent to the selected authors by 12th January 2024, with instructions for the expanded manuscript preparation for the conference proceedings. The deadline for submission of the final paper will be Early March, 2024 (TBC).

Please join the ICMTS LI group, if you have interest in all things test and measurement.

Details of the venue, hotel, registration, etc. will be posted when available at the ICMTS 2024 official website.

For further technical information, please contact the technical program chair:

Francesco Driussi, Università di Udine

3rd MFEM Community Workshop, October 26, 2023

- Arbitrary high-order finite element meshes and spaces.

- Wide variety of finite element discretization approaches.

- Conforming and nonconforming adaptive mesh refinement.

- Scalable from laptops to GPU-accelerated supercomputers.

- ... and many more.

- See MFEM Gallery, Publications, Videos and News pages.

If you plan to attend, please register no later than October 19th. There is no registration fee. Zoom details will be distributed to participants prior to the event date. For questions, please contact the meeting organizers at mfem@llnl.gov.

Sep 27, 2023

[paper] Model for Cryo-CMOS Subthreshold Swing

Sep 26, 2023

[paper] Characterization and Modeling of SOI LBJTs at 4K

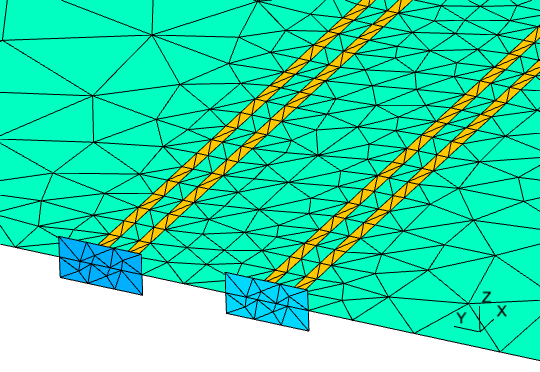

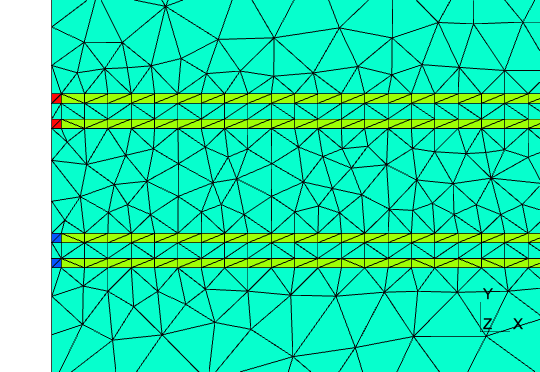

Palace: 3D Finite Element Solver for Computational Electromagnetics

Palace, for PArallel LArge-scale Computational Electromagnetics, is an open-source, parallel finite element code for full-wave 3D electromagnetic simulations in the frequency or time domain, using the MFEM finite element discretization library.Key features:

- Eigenmode calculations with optional material or radiative loss including lumped impedance boundaries. Automatic postprocessing of energy-participation ratios (EPRs) for circuit quantization and interface or bulk participation ratios for predicting dielectric loss.

- Frequency domain driven simulations with surface current excitation and lumped or numeric wave port boundaries. Wideband frequency response calculation using uniform frequency space sampling or an adaptive fast frequency sweep algorithm.

- Explicit or fully-implicit time domain solver for transient electromagnetic analysis.

- Lumped capacitance and inductance matrix extraction via electrostatic and magnetostatic problem formulations.

- Support for a wide range of mesh file formats for structured and unstructured meshes, with built-in uniform or region-based parallel mesh refinement.

- Arbitrary high-order finite element spaces and curvilinear mesh support thanks to the MFEM library.

- Scalable algorithms for the solution of linear systems of equations, including geometric multigrid (GMG), parallel sparse direct solvers, and algebraic multigrid (AMG) preconditioners, for fast performance on platforms ranging from laptops to HPC systems.

Sep 25, 2023

[workshop] gdsfactory

The first gdsfactory hands-on workshop organized as part of the UCSB Photonics Society. Thomas Dorch from Freedom Photonics and Andrei Isichenko presented gdsfactory. Last year gdsfactory seminar by Joaquin Matres, the maintainer of gdsfactory - you can access the video recording here. This workshop was a hands on; things to do before the workshop

- Install anaconda python 3 on your computer. If you don't have it installed, the links below are for miniconda, a "lightweight" version of anaconda. Windows: link. Mac: link (select if Intel or M1).

- Download a Python IDE. Either Visual Studio Code or Pycharm. Personally I prefer VS Code

- Download klayout. Windows: link. Mac: link (works on M1 mac, Ventura 13.4).

gdsfactory team will be running the tutorial using python notebooks (.ipynb). These can be run through JupyterLab, VS code (install this extension), or through Google Colab. You have the option to skip all the steps above and run the notebooks entirely in Google Colab (but with some limitations in klayout integration). You can try it out using this notebooks in this repository, focused on workshop_part1.ipynb. In Google Drive you should have the option to select "open with Google Colaboratory"

Click the "Open in Colab" link above to get started, and save a copy of the notebook to your Google Drive.

Google Drive Links to the notebooks:

https://drive.google.com/file/d/1x6kHQ9nHb1HB4HOEiEr1BG_y5lQ8si3e/view?usp=sharing

https://drive.google.com/file/d/1Ppz-CDrFezfLTIAHeBLYopl6Q4oyt8a4/view?usp=sharing

Sep 18, 2023

[Workshop] QIP

Silicon Quantum Information Processing (QIP) is highly appealing due to excellent spin qubit performances and the expertise of the integrated circuit industry in device scaling. Demonstrations of long-lived, high-fidelity silicon qubits, multi-qubit gates and spin–photon coupling, are promising for the control and interconnect of QIP architectures. Recently, spin qubits in related semiconductors (e.g. germanium) have also emerged as promising implementations of scalable quantum hardware. The formidable challenge of scaling these systems to the level required for meaningful computational applications has also brought to the fore the need for robust cryo-CMOS electronics, which will enable fast control and data processing, as well as schemes to correct errors and protect against decoherence. This meeting will bring together leading researchers from the QIP communities of silicon and related semiconductors, as well as cryo-CMOS designers and engineers who are working at different layers of the “quantum stack”.

| 10:00AM- 10:10AM | Introduction |

| 10:10AM- 10:40AM |

Pablo Cova Farina Quantum dot ladders for quantum computation and simulation

|

| 10:40AM-11:00AM |

Federico Fedele Automatic techniques for fast and automatic all-rf tuning of quantum devices

|

| 11:00AM-11:30AM |

Mark Johnson Rapid characterisation of over 1000 silicon quantum dots

|

| 11:30AM-11:50AM | Break and refreshments |

| 11:50AM-12:20PM |

Gian Salis How are hole-spin qubits in Ge/SiGe heterostructures driven and why do they decohere?

|

| 12:20PM-12:40PM |

Ross Leon Exchange control in a MOS double quantum dot made on a 300mm process

|

| 12:40PM-1:10PM |

Asen Asenov A Methodology for Cryogenic PDK Re-Centering Using Experimental Data and TCAD Simulations

|

| 1:10PM-2:30PM |

Lunch

|

| 2:30PM-3:00PM |

Masoud Babaie A Cryo-CMOS Receiver for Spin Qubit Gate-Based Readout: from Modelling to Implementation and Verification

|

| 3:00PM-3:20PM |

Mathieu de Krujif Measurement of classical electronics heating a local quantum dot thermometer in silicon

|

| 3:20PM-3:40PM |

Janne Lehtinen Custom CMOS platform for quantum processor units

|

| 3:40PM-4:00PM |

Stavroula Kapoulea Towards the Development of Quantum Computing System-On-Chip: Bringing Electronics Closer to Qubits

|

| 4:00PM-4:10PM | Concluding remarks |

| 4:10PM-5:00PM | Refreshments |

| 5:00PM-6:00PM | Lab tour |

| 7:00PM-9:00PM | Conference Dinner |

Sep 10, 2023

[book] Advanced Ultra Low-Power Semiconductor Devices

Edited by Shubham Tayal, Abhishek Kumar Upadhyay, Shiromani Balmukund Rahi, and Young Suh Song

ISBN: 9781394166411 | (C)2023 Hardcover | 306 pages

Sep 8, 2023

[conference] 10th Micro Nano 2023

plenary speakers: https://2023.micro-nano.gr/plenary-speakers/and invited https://2023.micro-nano.gr/invited-speakers/

Dates to remember:

- Abstract submission deadline: September 18th, 2023

- Early-bird registration: October 9th, 2023

- Late poster presentation: October 23rd, 2023

- Special Event: Main Hall of the National and Kapodistrian University of Athens (Panepistimiou 30)

- Special Event (Nov.2): “40 years of Microelectronics in Greece”

https://2023.micro-nano.gr/special-event/

- Demokritos Congress Center, NCSR “Demokritos”

https://2023.micro-nano.gr/final-program/

On behalf of the Organizing Committee,

Prof. Margarita Chatzichristidi, Conference ChairDr. Eleni Makarona, Conference Co-chair

Conference e-mail address: MicroNano2023@chem.uoa.gr

Sep 5, 2023

[paper] VNWFET-based technology

Univ Lyon, ECL, INSA Lyon, CNRS, UCBL, CPE Lyon, INL, UMR5270, 69130 Ecully, France

Acknowledgment: This work has been founded by FVLLMONTI European Union’s Horizon 2020 research and innovation programme under grant agreement No 101016776.

Call for Book Chapters

[C4P] EDTM Conference 2024, Bangalore

Advances in modeling/simulation of devices, packages and processes; Technology CAD and benchmarking; Atomistic process and device simulation; Compact models for DTCO and STCO; AI/ML-augmented modelling; Material and interconnect modeling; Models for photonic devices.

- Three-page camera-ready paper submission starts: August 1,2023

- Paper submission deadline:

October 15, 2023October 30, 2023 - Notification for Acceptance: December 15, 2023

Accepted IEEE EDTM 2024 papers will be considered for competition for the Best Paper Award, Best Student Paper Awards and Best Poster Awards.

More details on paper submission can be found at the Paper Submission webpage.