Jean-Michel Sallese

Charge-based modeling of field effect transistors, Make it easy

Joint International EUROSOI and EuroSOI-ULIS Workshop (Sept.2020)

DOI: 10.1109/EuroSOI-ULIS53016.2021.956068

EDLab, EPFL, Lausanne (CH)

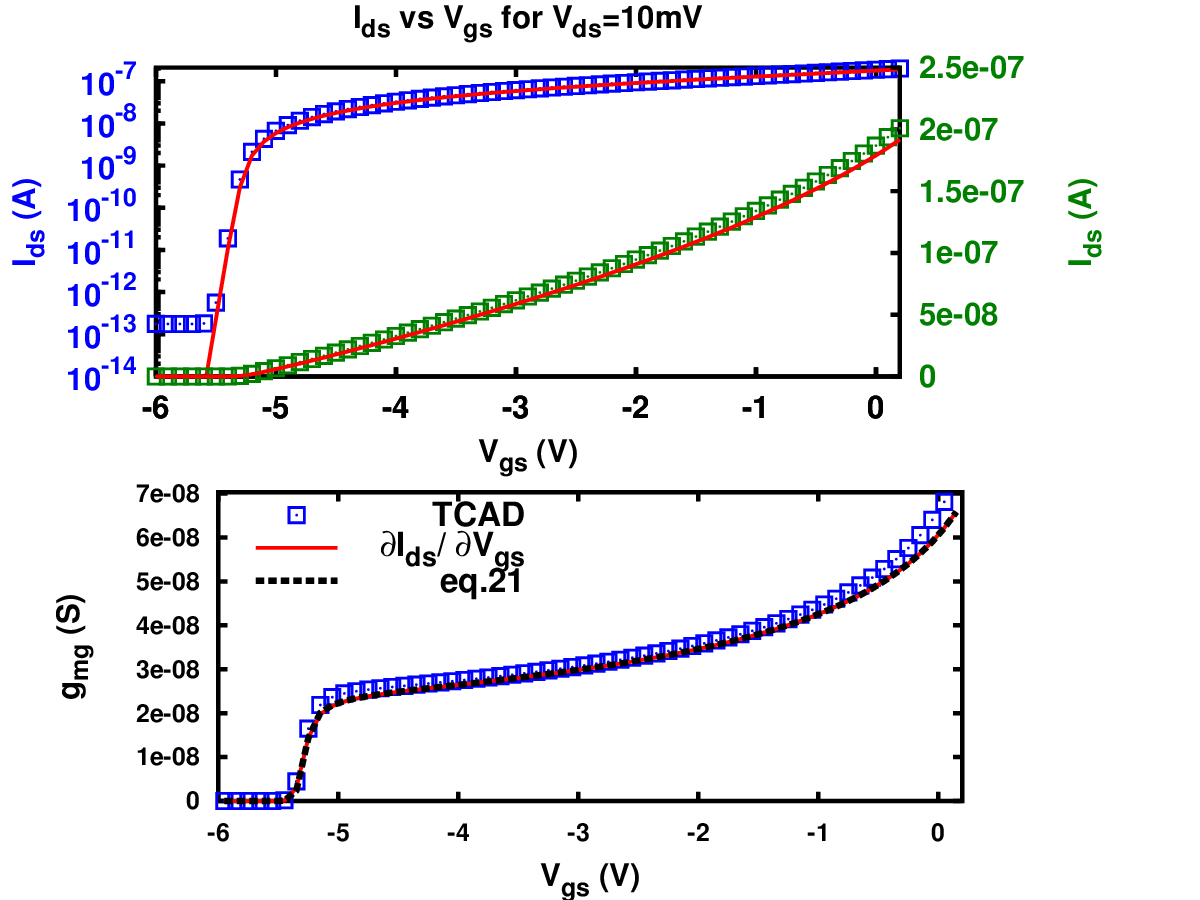

Abstract: In this presentation, we revisit some charge voltage dependencies for different architectures of field effect transistor, emphasizing on compactness and simplicity while maintaining a close link with physics, which makes these models predictive and accurate for general purposes of compact modeling.

Fig: The gm/I invariant versus the inversion coefficient

IC.

The operation modes of the MOSFET are clearly defined.