MOS-AK Workshop 2025 Held at London Metropolitan University [MOS-AK Media Note]

The MOS-AK Compact Modelling Workshop was successfully hosted on July 11, 2025, at London Metropolitan University, bringing together a diverse group of researchers, engineers, and industry professionals to explore recent advances in compact modelling, semiconductor technologies, and circuit simulation. This in-person event marked a valuable opportunity for participants to reconnect face-to-face, exchange ideas, and foster collaboration across institutions and disciplines.Open PDK Progress: "IHP-Open-PDK Review: Present Status and Future Directions" Dr. Krzysztof Herman - IHP Leibniz Institute for High Performance Microelectronics

Open PDK Progress: "The Application of FOSS Tools in the Design of IHP Open-Access 130nm BiCMOS RF Integrated Circuits" Prof. Mike Brinson - London Metropolitan University

Open PDK Progress: "Presentation and Evaluation of the 1st IHP Open Source Analog Certificate Course" Phillip Ferreira Baade-Pedersen - IHP Leibniz Institute for High Performance Microelectronics

Biomedical Sensing: "Non-invasive Biomedical Sensor for Dehydration Monitoring" Prof. Bal Virdee and Innocent Lubangakene London Metropolitan University (UK)

Quantum Modelling: "Compact Quantum Dot Models for Analog Microwave Co-Simulation"

Lorenzo Peri - Quantum Motion and University of CambridgeCryogenic Electronics: "Deep-Cryogenic Device Characterisation in a CMOS Foundry Process"

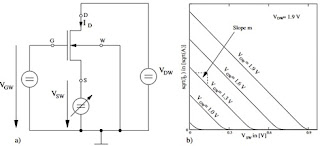

Grayson Noah - Quantum MotionCompact Modelling: "Developments of Compact Models for Source-Gated Devices"

Dr. Patryk Golec - École Polytechnique, ParisDisplay and Bio Circuits: "Area- and Energy-Efficient Current-Mode Pixel Circuits for High-Performance Display and Life Science Applications"

Dr. Eva Bestelink - University of SurreyNovel Transistor Behaviour: "Opportunities for Modelling Off-State Behaviour in Polysilicon Contact-Controlled Transistors"

Prof. Radu A. Sporea - University of Surrey

Each session stimulated thoughtful discussion and knowledge sharing among attendees, reinforcing the relevance of compact modelling in enabling innovation across semiconductor technologies.

The event was organized by London Metropolitan University with the support of the Institution of Engineering and Technology (IET) and the IEEE Electron Devices Society, and was generously sponsored by the IHP Leibniz Institute for High Performance Microelectronics.