As you may know SemiWiki published a book last year which is a really nice history of the fabless semiconductor ecosystem. Thousands of people have copies, we have received many compliments on it, and we are very proud.

As a thank you to all SemiWiki members I would like to offer a free PDF version of the book. You can access it via the attachment at the bottom of this wiki:

Fabless: The Transformation of the Semiconductor Industry

Only registered SemiWiki members can access this wiki so if you are not already a member please join as my guest:

https://www.semiwiki.com/forum/register.php

For those of you who are "seasoned" semiconductor professionals this book will be a nice walk down memory lane. If you are less seasoned it will be a great read to get you up to speed on how we got to where we are today and where we are going tomorrow, absolutely.

Sep 8, 2015

Sep 1, 2015

[video] How to Model a BJT Bipolar Junction Transistor

This video covers the basics of bipolar junction transistor (BJT) modeling and illustrates an easy step-by-step procedure to extract the model parameters of the popular Gummel-Poon (GP) model. While the GP model was introduced in the early 1970’s, it still enjoys a wide popularity in electronic device modeling and many modeling engineers consider it a classic and an excellent starting point for getting familiar with modeling in general.

Video Published on Aug 31, 2015

To download the project files referred to in this video visit:

http://www.keysight.com/find/eesof-how-to-model-BJT

Aug 17, 2015

Compact Modeling Marie Sklodowska-Curie Postdoctoral Fellowship in Spain

The European (Horizon 2020) Call for Postdoctoral Individual Marie Sklodowska-Curie Fellowships (H2020-MSCA-IF-2015) is open until September 10 2015.

I am looking for one or two candidates to work in my research group at the Universitat Rovira i Virgili (Tarragona, Spain) in the field of compact modeling of advanced semiconductor devices. Therefore, I would like to receive CVs from potential applicants. Once I have selected the candidates, we will make the application.

The candidates must have a Ph D in Electrical Engineering, Electronic Engineering, Physics, Telecommunication Engineering, or related subjects.

Candidates from all countries can apply for an Individual European Fellowship provided they have not sepent more than 12 months during the last 3 years in the country of the Host Institution (in this case, Spain)

These felowships can be for one or two years. Salaries are extremely good and the prestige of having this type of fellowship is very high. For this reason, there is a tough competition to get these fellowships.

I am looking for candidates for these Marie Curie Grants, both from Europe and outside Europe. Candidates must have a good CV (preferably with more than 4 publications as first author in international journals, in order to have chances). In order to fit the Marie Curie requirements, their age should be below 35.

If successful, the postdoctoral researchers will work on the characterization of compact modeling of any of the advanced semiconductor devices targeted by our research European projects: organic and oxide TFTs, advanced III-V HEMT and III-V MOSFETs, SOI and Multi-Gate MOSFETs, tunnel FETs.

The specific device/s in which the postdoctoral researcher will work will depend on his/her preference and background.

Candidates must send me by e-mail (to benjamin.iniguez@gmail.com) a CV or resume by AUGUST 31 2015. Successful applicants will be informed by SEPTEMBER 2, and then we will start to make the application. The successful candidates will be informed on the steps to do.

Tarragona is a small city (110000 inhabitants) on the Mediterranean coast, about 100 Km south from Barcelona, and very well connected to Barcelona and the main Spanish cities by rail and highway. Tarragona is a very old city, very important during the Roman Empire, and with a lot of historical landmarks.

The quality of life in Tarragona is excellent. Mediterranean and mild climate the whole year. Wonderful beaches around the city (even at the city). Mountains close to the city (even the Pyrenees are not far). Besides, the city is very quiet, but with an intense nightlife.

My research group in the Department of Electronic Engineering, Universitat Rovira i Virgili (URV) is one of the strongest groups in compact modeling in Europe. We are leading one European project on compact modeling of organic and oxide TFTs (in which a total of 9 European universities and companies participate). We also participate on other projects targeting other advanced devices.

I am looking forward to receiving excellent applications!

Benjamin IñiguezDepartment of Electronic Engineering

Tarragona, SPAIN

Universitat Rovira i Virgili (URV)

E-mail: benjamin.iniguez@gmail.com

I am looking for one or two candidates to work in my research group at the Universitat Rovira i Virgili (Tarragona, Spain) in the field of compact modeling of advanced semiconductor devices. Therefore, I would like to receive CVs from potential applicants. Once I have selected the candidates, we will make the application.

The candidates must have a Ph D in Electrical Engineering, Electronic Engineering, Physics, Telecommunication Engineering, or related subjects.

Candidates from all countries can apply for an Individual European Fellowship provided they have not sepent more than 12 months during the last 3 years in the country of the Host Institution (in this case, Spain)

These felowships can be for one or two years. Salaries are extremely good and the prestige of having this type of fellowship is very high. For this reason, there is a tough competition to get these fellowships.

I am looking for candidates for these Marie Curie Grants, both from Europe and outside Europe. Candidates must have a good CV (preferably with more than 4 publications as first author in international journals, in order to have chances). In order to fit the Marie Curie requirements, their age should be below 35.

If successful, the postdoctoral researchers will work on the characterization of compact modeling of any of the advanced semiconductor devices targeted by our research European projects: organic and oxide TFTs, advanced III-V HEMT and III-V MOSFETs, SOI and Multi-Gate MOSFETs, tunnel FETs.

The specific device/s in which the postdoctoral researcher will work will depend on his/her preference and background.

Candidates must send me by e-mail (to benjamin.iniguez@gmail.com) a CV or resume by AUGUST 31 2015. Successful applicants will be informed by SEPTEMBER 2, and then we will start to make the application. The successful candidates will be informed on the steps to do.

Tarragona is a small city (110000 inhabitants) on the Mediterranean coast, about 100 Km south from Barcelona, and very well connected to Barcelona and the main Spanish cities by rail and highway. Tarragona is a very old city, very important during the Roman Empire, and with a lot of historical landmarks.

The quality of life in Tarragona is excellent. Mediterranean and mild climate the whole year. Wonderful beaches around the city (even at the city). Mountains close to the city (even the Pyrenees are not far). Besides, the city is very quiet, but with an intense nightlife.

My research group in the Department of Electronic Engineering, Universitat Rovira i Virgili (URV) is one of the strongest groups in compact modeling in Europe. We are leading one European project on compact modeling of organic and oxide TFTs (in which a total of 9 European universities and companies participate). We also participate on other projects targeting other advanced devices.

I am looking forward to receiving excellent applications!

Benjamin IñiguezDepartment of Electronic Engineering

Tarragona, SPAIN

Universitat Rovira i Virgili (URV)

E-mail: benjamin.iniguez@gmail.com

Aug 10, 2015

ESSDERC ESSCIRC in Graz (A)

ESSDERC 2015: 45th European Solid-State Device Conference

ESSCIRC 2015: 41th European Solid-State Circuits Conference

September 14-18, 2015 - Graz, Austria

The aim of ESSDERC and ESSCIRC is to provide an annual European forum for the presentation and discussion of recent advances in solid-state devices and circuits. The increasing level of integration for system-on-chip design made available by advances in silicon technology is, more than ever before, calling for a deeper interaction among technologists, device experts, IC designers, and system designers. While keeping separate Technical Program Committees, ESSCIRC and ESSDERC are governed by a common Steering Committee and share Plenary Keynote Presentations and Joint Sessions bridging both communities. Attendees registered for either conference are encouraged to attend any of the scheduled parallel sessions, regardless to which conference they belong.

Read more:

- Program at a glance (Sept. 14 to 18, 2015 including Tutorials and Workshops)

- Program folder

Labels:

Circuits,

conference,

Device,

European,

mos-ak,

Solid-State

Location:

Graz, Austria

Aug 7, 2015

[mos-ak] [Final Program] Autumn 2015 MOS-AK Workshop at ESSDERC/ESSCIRC

Autumn 2015 MOS-AK Workshop at ESSDERC/ESSCIRC

Graz (A) September 18, 2015

Final Workshop Program

<http://www.mos-ak.org/graz_2015/>

Graz (A) September 18, 2015

Final Workshop Program

<http://www.mos-ak.org/graz_2015/>

Together with the MOS-AK Workshop Scientific Program Coordinators Larry Nagel and Andrei Vladimirescu, local workshop chairs Benjamin Iniguez, URV (SP) and Jean-Michel Sallese, EPFL (CH) as well as Extended MOS-AK TPC Committee, we have pleasure to invite to the MOS-AK Workshop which will be held in Graz (A) at the ESSDERC/ESSCIRC Conference following a joint modeling session (invited talks by Prof. C.C.Enz and Prof. C.Hu) as well as a session with regular modeling paper (and the invited talk by Prof. M.Lundstrom). Next MOS-AK/Graz workshop is organized with aims to strengthen a network and discussion forum among experts in the field, enhance open platform for information exchange related to compact/SPICE modeling and Verilog-A standardization, bring people in the compact modeling field together, as well as obtain feedback from technology developers, circuit designers, and CAD/EDA tool developers and vendors. All three modeling events would allow us to discuss all broad aspects of the compact/SPICE modeling and its Verilog-A standardization as well as highlighting important our research topics at such top level forum as the ESSCER/ESSCIRC Conferences. Already now, looking forward to meet you and all your industrial and academic partners in Graz, very soon.

Venue:

University of Technology,

Campus Inffeldgasse

Graz (A)

Campus Inffeldgasse

Graz (A)

Important Dates:

- Call for Papers - March 2015

- 2nd Announcement - May 2015

- Final Workshop Program - July 2015

- MOS-AK Workshop - Sept.18, 2015 <http://www.mos-ak.org/graz_2015/>

- 08:30 - 09:00 - On-site Registration

- 09:00 - 12:00 - Morning MOS-AK Session

- 12:00 - 13:00 - Lunch

- 13:00 - 16:00 - Afternoon MOS-AK Session

Selected best MOS-AK technical presentation will be recommended for further publication in a special issue of the International Journal of High Speed Electronics and Systems

Extended MOS-AK Committee

wg/aug/15

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To unsubscribe from this group and stop receiving emails from it, send an email to mos-ak+unsubscribe@googlegroups.com.

To post to this group, send email to mos-ak@googlegroups.com.

Visit this group at http://groups.google.com/group/mos-ak.

For more options, visit https://groups.google.com/d/optout.

Aug 6, 2015

Best Practices for Compact Modeling in Verilog-A

Mcandrew, C.C.; Coram, G.J.; Gullapalli, K.K.; Jones, J.R.; Nagel, L.; Roy, A.S.; Roychowdhury, J.; Scholten, A.J.; Smit, G.D.J.; Wang, X.; Yoshitomi, S., "Best Practices for Compact Modeling in Verilog-A," Electron Devices Society, IEEE Journal of the , vol.PP, no.99, pp.1,1

doi: 10.1109/JEDS.2015.2455342

keywords: Capacitance, Computational modeling, Convergence, Hardware design languages, Integrated circuit modeling, Mathematical model, Numerical models

[read more...]

REFERENCES[1] S. Liu, K. C. Hsu, and P. Subramaniam, “ADMIT-ADVICE modeling interface tool,” Proc. IEEE Customs Integrated Circuits Conf., pp. 6.6.1- 6.6.4, 1988.

[2] M. Vlach, “Modeling and simulation with Saber,” Proc. 3rd Annual ASIC Seminar and Exhibit, pp. T11.1-T11.9, 1990.

[3] E. McReynolds, personal communication, circa 1995.

[4] E. Christen and K. Bakalar, “VHDL-AMS—A hardware description language for analog and mixed-signal applications,” IEEE Trans. Circuits and Systems II, vol. 46, no. 10, pp. 1263-1272, Oct. 1999.

[5] [Online]: http://www.accellera.org/downloads/standards/v-ams (accessed June, 2015).

[6] L. Lemaitre, G. Coram, C. McAndrew, and K. Kundert, “Extensions to Verilog-A to support compact device modeling,” Proc. IEEE Behavioral Modeling and Simulation Workshop, pp. 134-138, Oct. 2003.

[7] L. Zhou, B. P. Hu, B. Wan, and C.-J. R. Shi, “Rapid BSIM model implementation with VHDL-AMS/Verilog-AMS and MCAST compact

model compiler,” IEEE Int. SOC Conf., pp. 285-286, Sep. 2003.

[8] G. Coram and M. Ding, “Recent achievements in Verilog-A compact modeling,” MOS-AK Workshop, Dec. 2009.

[9] G. Coram, “How to (and how not to) write a compact model in Verilog- A,” Proc. IEEE Behavioral Modeling a Simulation Workshop, pp. 97-106, Oct. 2004.

[10] G. Coram and C. C. McAndrew, “Verilog-A for compact modeling: best practices for high-quality model authoring,” Workshop on Compact Modeling for RF, Sep. 2005.

[11] G. Coram, “Verilog-A: an introduction for compact modelers,” MOS-AK Workshop, Sep. 2006.

[12] M. Mierzwinski, P. O’Halloran, and B. Troyanovsky, “Developing and releasing compact models using Verilog-A,” MOS-AK Workshop, Dec. 2008.

[13] G. Depeyrot and F. Poullet, “Guidelines for Verilog-A compact model coding,” MOS-AK Workshop, Sep. 2009.

[14] M. Mierzwinski, P. O’Halloran, and B. Troyanovsky, “Practical considerations for developing, debugging, and releasing Verilog-A models,” MOS-AK Workshop, Dec. 2009.

[15] C. C. McAndrew and G. Coram, “General and junction primitives for Verilog-A compact models,” nanoHUB. doi:10.4231/D3G15TC2J, 2015.

[16] C. C. McAndrew, “R3,” nanoHUB. doi:10.4231/D3QB9V64G, 2014.

[17] L. W. Nagel, SPICE2: A Computer Program to Simulate Semiconductor Circuits, Memo. ERL-M520, Univ. California, Berkeley, May 1975.

[18] X. Li, W. Wu, G. Gildenblat, C. C. McAndrew, and A. J. Scholten, “Benchmark tests for MOSFET compact models,” in Compact Modeling: Principles, Techniques and Applications, G. Gildenblat (Ed), Springer, pp. 75-104, 2010

[19] Y. Tsividis and C. McAndrew, Operation and Modeling of the MOS Transistor, 3rd ed., New York: Oxford University Press, 2011.

[20] [Online]: http://physics.nist.gov/cuu/Constants/Citations/Search.html (accessed June, 2015)

[21] A. Parker, “Getting to the heart of the matter,” IEEE Microwave Magazine, vol. 16, no. 3, pp. 76-86, Apr. 2015. [22] H. K. Dirks, Kapazit¨atskoeffizienten nichtlinearer dissipativer Systeme, Habilitation Theses, RWTH Aachen University, 1998.

[23] A. C. T. Aarts, R. van der Hout, J. C. J. Paasschens, A. J. Scholten, M. B. Willemsen, and D. B. M. Klaassen, “New fundamental insights into capacitance modeling of laterally nonuniform MOS devices,” IEEE Trans. Electron Dev., vol. 53, no. 2, pp. 270-278, Feb. 2006.

[24] C. C. McAndrew, “Practical modeling for circuit simulation,” IEEE J. Solid-State Circuits, vol. 33, no. 3, pp. 439-448, Mar. 1998.

[25] C. C. McAndrew, “Useful numerical techniques for compact modeling,” Proc. IEEE ICMTS, pp. 121-126, Apr. 2002. [26] K. Kundert, “Hidden state in SpectreRF,” [Online]: http://http://www.designers-guide.org/analysis/hidden-state.pdf (accessed June, 2015)

[27] R. K. Johnson, The Elements of MATLAB R⃝ Style, Cambridge University Press, 2011.

[28] M. Driessen and D. B. M. Klaassen, personal communication, 2006.

[29] [Online]: https://nanohub.org/groups/needs (accessed June, 2015)

[30] L. Lemaitre, C. C. McAndrew, and S. Hamm, “ADMS-automated device model synthesizer,” Proc. IEEE CICC, pp. 27-30, May 2002.

[31] [Online]: http://sourceforge.net/projects/mot-adms/ (accessed June, 2015)

doi: 10.1109/JEDS.2015.2455342

Abstract: Verilog-A is the de facto standard language that the semiconductor industry uses to define compact models. Unfortunately, it is easy to write models poorly in Verilog-A, and this can lead to unphysical model behavior, poor convergence, and difficulty in understanding and maintaining model codes. This paper details best practices for writing compact models in Verilog-A, to try to help raise the quality of compact modeling throughout the industry.

keywords: Capacitance, Computational modeling, Convergence, Hardware design languages, Integrated circuit modeling, Mathematical model, Numerical models

[read more...]

REFERENCES[1] S. Liu, K. C. Hsu, and P. Subramaniam, “ADMIT-ADVICE modeling interface tool,” Proc. IEEE Customs Integrated Circuits Conf., pp. 6.6.1- 6.6.4, 1988.

[2] M. Vlach, “Modeling and simulation with Saber,” Proc. 3rd Annual ASIC Seminar and Exhibit, pp. T11.1-T11.9, 1990.

[3] E. McReynolds, personal communication, circa 1995.

[4] E. Christen and K. Bakalar, “VHDL-AMS—A hardware description language for analog and mixed-signal applications,” IEEE Trans. Circuits and Systems II, vol. 46, no. 10, pp. 1263-1272, Oct. 1999.

[5] [Online]: http://www.accellera.org/downloads/standards/v-ams (accessed June, 2015).

[6] L. Lemaitre, G. Coram, C. McAndrew, and K. Kundert, “Extensions to Verilog-A to support compact device modeling,” Proc. IEEE Behavioral Modeling and Simulation Workshop, pp. 134-138, Oct. 2003.

[7] L. Zhou, B. P. Hu, B. Wan, and C.-J. R. Shi, “Rapid BSIM model implementation with VHDL-AMS/Verilog-AMS and MCAST compact

model compiler,” IEEE Int. SOC Conf., pp. 285-286, Sep. 2003.

[8] G. Coram and M. Ding, “Recent achievements in Verilog-A compact modeling,” MOS-AK Workshop, Dec. 2009.

[9] G. Coram, “How to (and how not to) write a compact model in Verilog- A,” Proc. IEEE Behavioral Modeling a Simulation Workshop, pp. 97-106, Oct. 2004.

[10] G. Coram and C. C. McAndrew, “Verilog-A for compact modeling: best practices for high-quality model authoring,” Workshop on Compact Modeling for RF, Sep. 2005.

[11] G. Coram, “Verilog-A: an introduction for compact modelers,” MOS-AK Workshop, Sep. 2006.

[12] M. Mierzwinski, P. O’Halloran, and B. Troyanovsky, “Developing and releasing compact models using Verilog-A,” MOS-AK Workshop, Dec. 2008.

[13] G. Depeyrot and F. Poullet, “Guidelines for Verilog-A compact model coding,” MOS-AK Workshop, Sep. 2009.

[14] M. Mierzwinski, P. O’Halloran, and B. Troyanovsky, “Practical considerations for developing, debugging, and releasing Verilog-A models,” MOS-AK Workshop, Dec. 2009.

[15] C. C. McAndrew and G. Coram, “General and junction primitives for Verilog-A compact models,” nanoHUB. doi:10.4231/D3G15TC2J, 2015.

[16] C. C. McAndrew, “R3,” nanoHUB. doi:10.4231/D3QB9V64G, 2014.

[17] L. W. Nagel, SPICE2: A Computer Program to Simulate Semiconductor Circuits, Memo. ERL-M520, Univ. California, Berkeley, May 1975.

[18] X. Li, W. Wu, G. Gildenblat, C. C. McAndrew, and A. J. Scholten, “Benchmark tests for MOSFET compact models,” in Compact Modeling: Principles, Techniques and Applications, G. Gildenblat (Ed), Springer, pp. 75-104, 2010

[19] Y. Tsividis and C. McAndrew, Operation and Modeling of the MOS Transistor, 3rd ed., New York: Oxford University Press, 2011.

[20] [Online]: http://physics.nist.gov/cuu/Constants/Citations/Search.html (accessed June, 2015)

[21] A. Parker, “Getting to the heart of the matter,” IEEE Microwave Magazine, vol. 16, no. 3, pp. 76-86, Apr. 2015. [22] H. K. Dirks, Kapazit¨atskoeffizienten nichtlinearer dissipativer Systeme, Habilitation Theses, RWTH Aachen University, 1998.

[23] A. C. T. Aarts, R. van der Hout, J. C. J. Paasschens, A. J. Scholten, M. B. Willemsen, and D. B. M. Klaassen, “New fundamental insights into capacitance modeling of laterally nonuniform MOS devices,” IEEE Trans. Electron Dev., vol. 53, no. 2, pp. 270-278, Feb. 2006.

[24] C. C. McAndrew, “Practical modeling for circuit simulation,” IEEE J. Solid-State Circuits, vol. 33, no. 3, pp. 439-448, Mar. 1998.

[25] C. C. McAndrew, “Useful numerical techniques for compact modeling,” Proc. IEEE ICMTS, pp. 121-126, Apr. 2002. [26] K. Kundert, “Hidden state in SpectreRF,” [Online]: http://http://www.designers-guide.org/analysis/hidden-state.pdf (accessed June, 2015)

[27] R. K. Johnson, The Elements of MATLAB R⃝ Style, Cambridge University Press, 2011.

[28] M. Driessen and D. B. M. Klaassen, personal communication, 2006.

[29] [Online]: https://nanohub.org/groups/needs (accessed June, 2015)

[30] L. Lemaitre, C. C. McAndrew, and S. Hamm, “ADMS-automated device model synthesizer,” Proc. IEEE CICC, pp. 27-30, May 2002.

[31] [Online]: http://sourceforge.net/projects/mot-adms/ (accessed June, 2015)

Jul 10, 2015

Octave-Forge Community Choice POTM

The Octave-Forge packages -- Community Choice Project of the Month for July

For one of the July "Community Choice" Projects of the Month, the community elected Octave-Forge, a central location for the collaborative development of packages for GNU Octave, a high-level interpreted language. The Octave-Forge packages expand Octave's core functionality by providing field specific features via Octave's package system. Some of the individual Octave-Forge packages include: image and signal processing, fuzzy logic, instrument control, and statistics packages.

Download Octave-Forge now.

Related Projects:

For one of the July "Community Choice" Projects of the Month, the community elected Octave-Forge, a central location for the collaborative development of packages for GNU Octave, a high-level interpreted language. The Octave-Forge packages expand Octave's core functionality by providing field specific features via Octave's package system. Some of the individual Octave-Forge packages include: image and signal processing, fuzzy logic, instrument control, and statistics packages.

Download Octave-Forge now.

Related Projects:

- VFreeMat--An interpreted, matrix-oriented development environment for engineering and scientific applications.

- AquaTerm--A Mac OS X grahics renderer.

- Quite Universal Circuit Simulator--A circuit simulator with graphical user interface (GUI)

Jun 30, 2015

Analog CMOS from 5 micrometer to 5 nanometer

Sansen, W., "1.3 Analog CMOS from 5 micrometer to 5 nanometer," ISSCC 2015 IEEE International , vol., no., pp.1,6, 22-26 Feb. 2015 doi: 10.1109/ISSCC.2015.7062848

Abstract: In our future, as usual, analog designers will continue to expand their expertise and knowledge in response to changing needs. While devices will change their nature and operate at higher and higher frequencies, their I-V characteristics will remain similar. In the near term, increased speed of MOS circuits, will be reached by operating deeper in weak inversion. Offset and 1/f noise will continue to play a critical role. Thus, in general, it seems that analog expertise is insensitive to technology change.

[read more]

Jun 29, 2015

QUCS: Project of the Week, June 1, 2015

The Qucs is one of the featured projects for the week (June 1, 2015), which appear on the front page of SourceForge.net:

Qucs is a circuit simulator with a graphical user interface. The software aims to support all kinds of circuit simulation types such as, e.g. DC, AC, S-parameter, Transient, Noise, and Harmonic Balance analysis. Pure digital simulations are also supported.

[ Download Quite Universal Circuit Simulator ]

Qucs is a circuit simulator with a graphical user interface. The software aims to support all kinds of circuit simulation types such as, e.g. DC, AC, S-parameter, Transient, Noise, and Harmonic Balance analysis. Pure digital simulations are also supported.

[ Download Quite Universal Circuit Simulator ]

Labels:

AC,

compact modeling,

DC,

FOSS,

Harmonic Balance,

noise,

open source,

QUCS,

Transient

Jun 17, 2015

3rd Training Course on Compact Modeling

3rd TCCM,

organized as IEEE EDS Mini-Colloquium

(http://eds.ieee.org/lectures.html?eid=136)

(http://eds.ieee.org/lectures.html?eid=136)

Co-organizer: Institute of Electron Technology, Warsaw, Poland

Technical Program Promoter: DMCS, Lodz University of Technology, Łódź, Poland

Date: June 24, 2015.

Place: Hotel Bulwar (Lejda room) ul. Bulwar Filadelfijski 18, 87-100 Toruń, Poland

www: http://www.hotelbulwar.pl

Final schedule of TCCM:

9:00 Wladek Grabinski, Opening

9:10 Henryk Przewłocki, "Weaknesses and corrections of the classical theory of photoelectric phenomena in the MOS system"

10:00 Juin J.Liou, "Compact Modeling of Junction Failure in Semiconductor Devices Subject to Electrostatic Discharge Stresses"

10:50 Coffee break

11:10 Jean-Michel Sallese, "Modeling Junctionless Field Effect Transistors"

12:00 Mike Brinson, "A unified approach to compact device modelling with the open source packages Qucs/ADMS and MAPP/Octave"

13:00 Lunch

14:30 Benjamin Iniguez, "Physically-Based Compact Modeling of GaN HEMT"

15:20 Wladek Grabinski, "Verilog-A Compact Model Standardization"

16:10 Daniel Tomaszewski, "Compact modeling and statistical modeling for parametric yield improvement"

17:00 Wladek Grabinski, Closing

Labels:

CAD,

COMON,

compact modeling,

EDS,

GNU,

IEEE,

MIXDES,

open source,

Qucs; MOSFET; Verilog-A,

TCCM

Jun 12, 2015

Micro&Nano 2015 - 2nd Announcement

6th Micro & Nano Conference on Micro - Nanoelectronics, Nanotechnologies and MEMs

4-7 October, 2015, Athens, Greece

http://conference-micronano2015.micro-nano.gr

4-7 October, 2015, Athens, Greece

http://conference-micronano2015.micro-nano.gr

Second Announcement

The "Micro&Nano 2015" Conference will be held at the Fenix Hotel, in Glyfada, Athens, Greece. The Best Western Hotel Fenix is conveniently located in Glyfada, an attractive resort in the south coast of Athens. More details on the Conference venue can be found on the conference website:

<http://conference-micronano2015.micro-nano.gr>Conference Topics:

- Micro and Nano- Fabrication

- Materials for Electronics, Photonics and Sensors

- Electronic, Optoelectronic and Photonic Devices

- Sensors and Actuators

All abstracts should not exceed the limit of 300 words. Please follow the abstract template that can be found here. The deadline for abstract submission is on 30 June 2015.

The Conference abstracts will be published in the "Abstract Book" that will be distributed to all the participants, at the beginning of the Conference. Selected papers will be published, after peer-review, in special issues of the following international journals:

- Nanoscale Research Letters (the nanoscience related articles)

- Microelectronic Engineering

May 15, 2015

[mos-ak] [2nd Announcement and Call for Papers] Autumn 2015 MOS-AK Workshop at ESSDERC/ESSCIRC

Autumn 2015 MOS-AK Workshop at ESSDERC/ESSCIRC

Graz (A) September 18, 2015

2nd Announcement and Call for Papers

Graz (A) September 18, 2015

2nd Announcement and Call for Papers

Together with the MOS-AK Workshop Scientific Program Coordinators Larry Nagel and Andrei Vladimirescu, local workshop chairs Benjamin Iniguez, URV (SP) and Jean-Michel Sallese, EPFL (CH) as well as Extended MOS-AK TPC Committee, we have pleasure to invite to the MOS-AK Workshop which will be held in Graz (A) at the ESSDERC/ESSCIRC Conference where also a joint modeling session (invited talks by Prof. C.C.Enz and Prof. C.Hu) as well as a session with regular modeling paper (and the invited talk by Prof. M.Lundstrom) are planed. Following MOS-AK workshop is organized with aims to strengthen a network and discussion forum among experts in the field, enhance open platform for information exchange related to compact/SPICE modeling and Verilog-A standardization, bring people in the compact modeling field together, as well as obtain feedback from technology developers, circuit designers, and CAD/EDA tool developers and vendors.

Venue:

University of Technology,

Campus Inffeldgasse

Graz (A)

Campus Inffeldgasse

Graz (A)

Important Dates:

- Call for Papers - March 2015

- 2nd Announcement - May 2015

- Final Workshop Program - July 2015

- MOS-AK Workshop - Sept.18, 2015

- 08:30 - 09:00 - On-site Registration

- 09:00 - 10:30 - Morning MOS-AK Session

- 11:00 - 12:00 - CM Standardization Pannel

- 12:00 - 13:00 - Lunch

- 13:00 - 16:00 - Afternoon MOS-AK Session

- Advances in semiconductor technologies and processing

- Compact Modeling (CM) of the electron devices

- Verilog-A language for CM standardization

- New CM techniques and extraction software

- Open Source TCAD/EDA modeling and simulation

- CM of passive, active, sensors and actuators

- Emerging Devices, CMOS and SOI-based memory cells

- Microwave, RF device modeling, high voltage device modeling

- Nanoscale CMOS devices and circuits

- Technology R&D, DFY, DFT and IC Designs

- Foundry/Fabless Interface Strategies

Authors should submit an abstract using on-line MOS-AK submission form

(any related inquiries can be sent to abstracts@mos-ak.org)

http://www.mos-ak.org/graz_2015/abstracts.php

Free online workshop registration:

(any related inquiries can be sent to register@mos-ak.org)

http://www.mos-ak.org/graz2015/registration.php

Postworkshop publications:

Selected best MOS-AK technical presentation will be recommended for further publication in a special issue of the International Journal of High Speed Electronics and Systems

Extended MOS-AK Committee

WG052015

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To unsubscribe from this group and stop receiving emails from it, send an email to mos-ak+unsubscribe@googlegroups.com.

To post to this group, send email to mos-ak@googlegroups.com.

Visit this group at http://groups.google.com/group/mos-ak.

For more options, visit https://groups.google.com/d/optout.

Mar 16, 2015

[MOS-AK/DATE 2015 Workshop] CEA-Leti's predictive model takes FDSOI further

CEA-Leti's predictive model takes FDSOI further

Fully Depleted Silicon On Insulator (FDSOI) is a planar process technology that relies on two primary innovations. First, an ultra-thin layer of insulator, called the buried oxide, is positioned on top of the base silicon.

Then, a very thin silicon film implements the transistor channel. Thanks to its thinness, there is no need to dope the channel, thus making the transistor fully depleted. The combination of these two innovations is called “ultra-thin body and buried oxide Fully Depleted SOI” or UTBB-FDSOI.

Back in 2013, CEA-Leti had deployed a first compact model, but working in close cooperation with STMicroelectronics, the research lab understood that more subtle back gate channelling effects had to be addressed to fully exploit the benefits of UTBB-FDSOI and to explore the transistors’ behaviour in more details.

New analytical equations were written from scratch for the Leti-UTSOI2.1 compact model, improving on the predictability and accuracy capabilities of the previous version, Leti-UTSOI2.

To date, other models from the University of Hiroshima, and from the University of Berkeley fail to account for inversion effects at the back interface, when a strong forward back bias (FBB) is applied, told us Thierry Poiroux, Leti research engineer and model co-developer.

More specifically, the French lab used a unique analytical resolution scheme for the calculation of surface potentials at both interfaces of the transistor body, offering a refined description of narrow-channel effects, with an improved accuracy of moderate inversion regime and gate tunnelling current modelling.

Because the model is analytical, it is much faster than any numerical simulation. It is now available in all major SPICE and Fast SPICE simulators through licences with EDA vendors and will allow fabless companies and IC designers to virtually explore different UTBB-FDSOI parameters within a given foundry process node. The new model can also be used by foundries and fabless companies to perform a predictive analysis of future nodes to come, in order to orient their ongoing process optimization.

for more information visit CEA-Leti at www.leti.fr

Location:

Grenoble, France

Mar 8, 2015

[BOOK] FinFET Modeling for IC Simulation and Design Using the BSIM-CMG Standard

FinFET Modeling for IC Simulation and Design Using the BSIM-CMG Standard

Yogesh Singh Chauhan, Darsen Lu, Sriramkumar Venugopalan, Sourabh Khandelwal, Juan Pablo Duarte, Navid Paydavosi, Ai Niknejad, Chenming Hu

Yogesh Singh Chauhan, Darsen Lu, Sriramkumar Venugopalan, Sourabh Khandelwal, Juan Pablo Duarte, Navid Paydavosi, Ai Niknejad, Chenming Hu

DESCRIPTIONThis book is the first to explain FinFET modeling for IC simulation and the industry standard – BSIM-CMG - describing the rush in demand for advancing the technology from planar to 3D architecture, as now enabled by the approved industry standard. The book gives a strong foundation on the physics and operation of FinFET, details aspects of the BSIM-CMG model such as surface potential, charge and current calculations, and includes a dedicated chapter on parameter extraction procedures, providing a step-by-step approach for the efficient extraction of model parameters.

KEY FEATURES

- Learn how to do FinFET modeling using the BSIM-CMG standard from the experts

- Authored by the lead inventor and developer of FinFET, and developers of the BSIM-CMG standard model, providing an experts’ insight into the specifications of the standard

- The first book on the industry-standard FinFET model - BSIM-CMG

- Why you should use FinFET

- The physics and operation of FinFET

- Details of the FinFET standard model (BSIM-CMG)

- Parameter extraction in BSIM-CMG

- FinFET circuit design and simulation

http://store.elsevier.com/product.jsp?isbn=9780124200319

http://www.amazon.com/FinFET-Modeling-IC-Simulation-Design/dp/0124200311

http://www.amazon.in/FinFET-Modeling-IC-Simulation-Design/dp/0124200311

Feb 17, 2015

MIXDES 2015, June 25-27, 2015; Torun, Poland

22nd International Conference "Mixed Design of Integrated Circuits and Systems"

MIXDES 2015, June 25-27, 2015; Torun, Poland

The deadline for regular paper submission is approaching (March 2nd, 2015). If you are going to contribute, I encourage you to register your papers as soon as possible. You will be able to update the paper details and the document file at any time till the final paper version deadline (May 15th, 2015). The early submission will allow us to take care of your paper just now, especially start the reviewer assignments and begin the formatting verification process.

[read more...]

Feb 16, 2015

Call for Papers [dvconeurope] DVCon-Europe 2015

DVCON EUROPE 2015

The Design and Verification Conference & Exhibition Europe (DVCon Europe) is the premier conference for system architects, concept engineers, software developers, design and verification engineers, and IP integrators to share the latest methodologies and technologies on the practical use of EDA and IP languages and standards used in electronic design.

The focus of this highly technical conference is on the industrial application of specialized design and verification languages such as SystemC, SystemVerilog, VHDL, UVM or e; assertions in SVA or PSL; the use of AMS languages; design automation using IP-XACT; and the use of general purpose languages C and C++.

CALL FOR PAPERS

This call for papers solicits presentations that are highly technical and reflect real life experiences in using EDA languages, standards, methodologies and tools. Industry applications of interest include (but are not limited to) automotive, mobile communication, aerospace, healthcare, chip-cards, consumer and power electronics. Submissions are encouraged in (but not restricted to) the four topic areas listed below. Low power techniques and design for functional safety (e.g., ISO 26262, DO-254) are pervasive and can be addressed in any of these topics areas.

Please submit your draft version of the paper by May 1, 2015. Detailed instructions on the paper requirements and submission process can be found on www.dvcon-europe.org.

Labels:

AMS languages,

standardization,

SystemC,

SystemVerilog,

Verilog,

VHDL

Location:

Munich, Germany

ESSCIRC/ESSDERC 2015 website is now active

ESSCIRC/ESSDERC 2015 website is now active: www.esscirc-essderc2015.org

The deadline for paper submission is 2 April, 2015.

Looking forward to seeing you in Graz!

Prof. Wolfgang Pribyl: General Chair ESSCIRC/ESSDERC 2015

Franz Dielacher, Gernot Hueber: ESSCIRC TPC Chairs

Martin Schrems, Tibor Grasser: ESSDERC TPC Chairs

The deadline for paper submission is 2 April, 2015.

Looking forward to seeing you in Graz!

Prof. Wolfgang Pribyl: General Chair ESSCIRC/ESSDERC 2015

Franz Dielacher, Gernot Hueber: ESSCIRC TPC Chairs

Martin Schrems, Tibor Grasser: ESSDERC TPC Chairs

Feb 12, 2015

Call for Papers: [fdl7] FDL2015

Forum on Specification & Design Languages

[fdl7] FDL 2015 CALL FOR PAPERS

September 14-16, 2015 | Barcelona, Spain

FDL is an international forum to exchange experiences and promote new trends in the application of languages, their associated design methods and tools for the design of electronic systems. FDL stimulates scientific and controversial discussions within and in-between scientific topics as described below. The program structure includes research working sessions, embedded tutorials, panels, and technical discussions. The Forum includes tutorials and fringe meetings, such as user group or standardization meetings. “Wild and Crazy Ideas” are also welcome.

Important Dates:

- Proposals for Special Session: March 22, 2015

- Full Research Paper submission: May 4, 2015

- Other Contributions submission: June 10, 2015

- Notification of acceptance: July 4, 2015

- Camera ready papers: August 12, 2015

[1st announcement] #SIXHackathon 20-21 March 2015 in Zurich (CH)

#SIXHackathon 20-21 March 2015 in Zurich (CH)

[1st announcement]

Are you interested in the financial technology sector (FinTech)? Are you on the lookout for a challenge? Then take part in SIX's Hackathon in Zurich 20 - 21 March 2015 and rub shoulders with one of the financial sector's leading IT companies for 30 hours.

What you can expect

Fun, challenging questions, exciting data sets, new ideas, networking opportunities, an exchange with like-minded people; people interested in FinTech and employees from SIX who are also participating.

What you have to do

SIX will provide you with data and APIs (interface information) from FinTech. You will work in small teams. The aim is to present an expert jury with a prototype or a concept after 30 hours. You can either select a topic freely or take inspiration from one of the workshops on big data in the financial technology sector and payment solutions. You will be competing against around 100 participants.

Who is eligible to take part

In principle, any student aged over 18 at a Swiss university or university of applied science and all SIX employees are eligible to take part. Participants must have an affinity and a relevant skill-set in the areas of software development, graphic or interface design, marketing, project management or similar.

Why it’s worth to participate

You will have the opportunity to prove your skills using real-life problems and present your ideas to an expert jury. Furthermore, SIX is searching for new talents – depending on your background, successful Hackathon participants could be offered a permanent position or a traineeship at SIX.

FOR MORE INFORMATION:

http://www.six-group.com/careers/en/site/hackathon.html

REGISTER NOW:

http://www.six-group.com/careers/en/site/hackathon/registration.html

Feb 10, 2015

Call for Papers: ESSCIRC/ESSDERC 2015 Graz (A)

the 41st ESSCIRC and 45th ESSDERC Conferences will take place on 14 to 18 September 2015 in Graz, Austria. The event is technically co-sponsored by the IEEE Electron Device Support and the IEEE Solid-State Circuit Society.

Detailed information about the conference will soon be provided at the ESSCIRC/ESSDERC 2015 website:

www.esscirc-essderc2015.org

The deadline for paper submission is 2 April, 2015

[read more...]

Detailed information about the conference will soon be provided at the ESSCIRC/ESSDERC 2015 website:

www.esscirc-essderc2015.org

The deadline for paper submission is 2 April, 2015

[read more...]

Feb 2, 2015

FOSS GPS watch

F*watch! Why should your watch be different?

(FOSS) F*watch is an infinitely hackable GPS watch with many sensors based on a 100% Free design. Everything is free, from the PCB and watch housing design to the software stack. Moreover, only free software FOSS tools have been used during the development.

The FOSDEM2015 talk described the development process and shows a first prototype, along with performance measurements and future plans.

FOSDEM2015 Speakers:

Links: F*Watch wiki

Jan 22, 2015

[mos-ak] [Announcement and Call for Papers] Spring 2015 MOS-AK Workshop at DATE

Spring 2015 MOS-AK Workshop at DATE

Grenoble March 12, 2015

Announcement and Call for Papers

Together with the MOS-AK Workshop Scientific Program Coordinators Larry Nagel and Andrei Vladimirescu, local workshop chairs Patrick Martin, CEA (F) and Benjamin Iniguez, URV (SP) as well as Extended MOS-AK TPC Committee, we have pleasure to invite to the Spring MOS-AK Workshop which will be held in Grenoble (F) at the DATE Conference. The event is organized with aims to strengthen a network and discussion forum among experts in the field, enhance open platform for information exchange related to compact/Spice modeling and Verilog-A standardization, bring people in the compact modeling field together, as well as obtain feedback from technology developers, circuit designers, and CAD/EDA tool developers and vendors.

Venue:

ALPEXPO-ALPES CongresParc Événementiel de GrenobleAvenue d'Innsbruck - CS 5240838034 Grenoble cedex 2; France

Important Dates:

Call for Papers - December 20142nd Announcement - January 2015Final Workshop Program - February. 2015MOS-AK Workshop - Friday, March 12, 2015

08:30 - 09:00 - On-site Registration09:00 - 11:00 - Morning MOS-AK Session11:00 - 12:00 - CM Standardization Panel12:00 - 13:00 - Lunch13:00 - 16:00 - Afternoon MOS-AK Session

- Advances in semiconductor technologies and processing

- Compact Modeling (CM) of the electron devices

- Verilog-A language for CM standardization

- New CM techniques and extraction software

- Open Source TCAD/EDA modeling and simulation

- CM of passive, active, sensors and actuators

- Emerging Devices, CMOS and SOI-based memory cells

- Microwave, RF device modeling, high voltage device modeling

- Nanoscale CMOS devices and circuits

- Technology R&D, DFY, DFT and IC Designs

- Foundry/Fabless Interface Strategies

Authors should submit an abstract using on-line MOS-AK submission form

(any related inquiries can be sent to wladek@grabinski.ch)

http://www.mos-ak.org/grenoble_2015/abstracts.php

Free online workshop registration:

http://www.mos-ak.org/grenoble_2015/abstracts.php

Free online workshop registration:

(any related inquiries can be sent to wladek@grabinski.ch)

http://www.mos-ak.org/grenoble_2015/registration.php

Postworkshop publications:

Selected best MOS-AK technical presentation will be recommended for further publication in a special issue of the International Journal of High Speed Electronics and Systems

Extended MOS-AK/GSA Committee

Postworkshop publications:

Selected best MOS-AK technical presentation will be recommended for further publication in a special issue of the International Journal of High Speed Electronics and Systems

Extended MOS-AK/GSA Committee

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To unsubscribe from this group and stop receiving emails from it, send an email to mos-ak+unsubscribe@googlegroups.com.

To post to this group, send email to mos-ak@googlegroups.com.

Visit this group at http://groups.google.com/group/mos-ak.

For more options, visit https://groups.google.com/d/optout.

IEEE Magazine Pays Special Tribute to Professor Yannis Tsividis

To Electrical Engineering Professor Yannis Tsividis’ long roster of distinguished achievements, add one more: the latest issue of IEEE Solid-State Circuits Magazine is devoted to his remarkable career and strong influence in advancing analog and mixed-signal integrated circuits.

Tsividis, recently named the Edwin Howard Armstrong Professor of Electrical Engineering at Columbia, created the first fully integrated mixed-signal metal-oxide-semiconductor (MOS) operational amplifier, which became key to pulse-code modulation (PCM) voice codecs for telephony and helped spur the industry toward mixed analog-digital MOS integrated circuits for communications. The work of Tsividis and his students has resulted in multiple patents around the world and extensive applications at the device, circuit, and system levels as well as in enhanced computer simulation.

Of the honor, Tsividis said, “I was moved by the kind words of my colleagues and former students, and delighted at the opportunity to tell my story.”

Jan 10, 2015

postdoctoral positions in Compact Modeling in Tarragona (Spain)

As Professor in the Universitat Rovira i Virgili (Tarragona, Catalonia, Spain), I am going to apply for two or three postdoctoral position (funded by the Spanish Ministry and the Catalan Government) related to our research projects about Compact Modeling of semiconductor devices: in particular, the European Union -funded "DOMINO" project (of which I am the coordinator, and which targets modeling of organic and oxide TFTs), and our national projects addressing the modeling of GaN HEMTs and nanowire MOSFETs.

The candidate should be a person who holds a PhD as awarded within the five years prior to the date when the period for presentation of application forms closes. If the candidate does not hold a PhD yet, the deadline to be awarded a PhD is the date of publication of the Awarding Resolution web site.

The candidate should have enough research experience in the field of semiconductor devices, and must have a very good knowledge of the physics of electron devices. The research project to be carried out can be adapted to the candidate's profile. In any case, it will be related to the research projects in which we participate. Our contribution in these projects is the physics and modeling (in particular compact modeling) of the novel devices addressed by our projects: organic and oxide Thin Film Transistors (TFTs), GaN HEMTs, nanowire FETs, multi-gate MOSFETs (FinFETs, DG MOSFETs,...), ...

The postdoc positions, which will be a contract, will have a duration of 2-3 years. The net salary will be around 1900 Euro/months.

The candidate should be a person who holds a PhD as awarded within the five years prior to the date when the period for presentation of application forms closes. If the candidate does not hold a PhD yet, the deadline to be awarded a PhD is the date of publication of the Awarding Resolution web site.

The candidate should have enough research experience in the field of semiconductor devices, and must have a very good knowledge of the physics of electron devices. The research project to be carried out can be adapted to the candidate's profile. In any case, it will be related to the research projects in which we participate. Our contribution in these projects is the physics and modeling (in particular compact modeling) of the novel devices addressed by our projects: organic and oxide Thin Film Transistors (TFTs), GaN HEMTs, nanowire FETs, multi-gate MOSFETs (FinFETs, DG MOSFETs,...), ...

The postdoc positions, which will be a contract, will have a duration of 2-3 years. The net salary will be around 1900 Euro/months.

The postdoctoral researcher will work in the compact device team, led by Prof Benjamin Iñiguez, belonging to the Nanoelectronics and Photonics Systems Group (NEPHOS) in the Department of Electronic, Electrical and Automatic Control Engineering of the Universitat Rovira i Virgili (URV). This team is a worldwide well recognized pioneering group in the development of compact models for advanced and emerging semiconductor devices. The team has participated in a number of European Union funded projects aout this topic and has led some of them.

Interested applicants should send me their CV by e-mail.

DEADLINE TO RECEIVE APPLICATIONS: January 25 2015

MY E-MAIL ADDRESS IS: benjamin.iniguez@gmail.com

Address:

Benjamin Iñiguez

Nanoelectronics and Photonics Systrems Group (NEPHOS)

Department of Electronic Engineering

Universitat Rovira i Virgili (URV)

Avinguda dels Paisos Catalans 26

43007 Tarragona

SPAIN.

About Tarragona:

Interested applicants should send me their CV by e-mail.

DEADLINE TO RECEIVE APPLICATIONS: January 25 2015

MY E-MAIL ADDRESS IS: benjamin.iniguez@gmail.com

Address:

Benjamin Iñiguez

Nanoelectronics and Photonics Systrems Group (NEPHOS)

Department of Electronic Engineering

Universitat Rovira i Virgili (URV)

Avinguda dels Paisos Catalans 26

43007 Tarragona

SPAIN.

About Tarragona:

Tarragona is located on the Mediterranean, in the heart of the Costa Daurada, in the south of Catalonia, about 100 Km south from Barcelona. Tarragona is well connected to Barcelona by highway, and frequent trains and buses. It has also a direct bus connection with Barcelona Airport. Besides, it has high-speed rail connection with Madrid and Barcelona.

Tarraco (the Roman name for Tarragona) was one of the most important cities in the Roman Empire. F On 30 November 2000, the UNESCO committee officially declared the Roman archaeological complex of Tàrraco a World Heritage Site. This recognition is intended to help ensure the conservation of the monuments, as well as to introduce them to the broader international public. Among the citizens of Tarragona, it has moreover fomented knowledge of, pride in and respect for the city.

Speaking about Tarraco’s climate, the famous Roman poet Virgil wrote: “The climate blends and confuses the seasons singularly, so that all the year seems an eternal spring.” Thanks to its temperate climate, with an average yearly temperature of 23ºC, its clean beaches with fine and gloden sand, and its singular artistic and architectural heritage, Tarragona is one of the most important tourism hubs in Europe. The city has a population of 120,202 inhabitants

Dec 5, 2014

Call for Papers PRIME 2015

The PRIME 2015 Call for Papers is available at:

http://web.eng.gla.ac.uk/prime2015/static/images/PRIME2015CFPv2.pdf

A Workshop is organized for all conference participants on June 29th. Moreover, a Company Fair is organized for all conference participants, to create a connection between major companies in Electronics/Microelectronics and Ph. D students.

PRIME 2015 topics of interest include, but are not limited, to:

- Micro/nanoelectronics

- Semiconductors

- Analog and Digital Signal Processing

- Computer Aided Design

- Analog, Digital, Mixed-Signal and RF IC Design

- Integrated Power ICs

- RF, Microwave and Millimeterwave Circuits

- VLSI and SoC Applications

- Visual Signal Processing

- Sensor Systems and MEMS

- Energy Scavenging

- Technical trends and challenges

- Electronic Skin

Dec 2, 2014

Meet with Silvaco at IEDM 2014

Silvaco will showcase at IEDM products for applications such as displays, power

devices, optical devices, advanced CMOS process development, radiation

& soft error reliability, analog and memory design.

- Victory Process, Device and Stress for 1D, 2D and 3D TCAD simulation for applications such as TFT displays, IGBT power devices, lasers, image sensors, advanced CMOS devices such as FDSOI and FinFETs, radiation and soft error reliability simulation

- Clever for 3D parasitic RC extraction with the highest accuracy capacitance extraction for application such as TFT design, FinFET SRAM analysis

- Utmost IV for creating SPICE models for any device type including TFT, UOTFT, BSIM-CMG for FinFETs, HSIM-HV2 for high voltage devices

- Affordable and complete custom design flow including schematic entry, layout, simulation, analysis and verification ideally suited to analog, power management applications and for process nodes such as 65nm/40nm that are key targets for Internet of Thing (IoT) designs

- SmartSpice for simulation of circuits such as analog/mixed-signal, HSIO, RF, SRAM, standard cells, TFT panels, power ICs and for which recent performance enhancement benchmark data will be shared

- SmartSpice for library, memory and critical path characterization with built-in optimizers and circuit rubber-banding capability, having achieved 16nm FinFET model certification and includes PODE and ETMI reliability model support

- SmartSpice Soft Error Reliability capability that is used to analyze the impact of Single Event Effects (SEE) on circuit performance, an increasingly important challenge at 20nm and below technology nodes

Nov 20, 2014

[mos-ak] FOSDEM 2015 Electronic Design Automation Devroom Call for Participation

This is the call for participation in the FOSDEM 2015 devroom on Free/Open Source Software (FOSS) Electronic Design Automation (EDA) tools, to be held on Sunday 1 February 2015 in Brussels, Belgium. We are looking for contributions under the form of talks covering the following main topics:

Spread the word!

This is the first EDA devroom at FOSDEM. Let's make sure as many projects and developers as possible are present. Thanks!

-- - Printed Circuit Board (PCB) design tools (e.g. KiCad and gEDA)

- High-level modelling tools for PCB and Hardware Description Language (HDL) design (e.g. Libre-FDATool)

- Analogue and digital simulators (e.g. ngspice, Qucs, Gnucap, Xyce, GHDL, Icarus and Verilator)

- Inter-project opportunities for collaboration

The submission process

Please submit your proposals at https://penta.fosdem.org/submission/FOSDEM15 before 1 December 2014.

If you already have a Pentabarf account (for example as a result of having submitted a proposal in the past), make sure you use it to log in and submit your proposal. Do not create a new account if you already have one. Please provide a bit of information about yourself in Person -> Biography. When you submit your proposal (creating an "Event" in Pentabarf), make sure you choose the "Electronic design automation devroom" in the track drop-down menu. Otherwise your proposal might go unnoticed. Fill in at least a title and abstract for the proposed talk and a suggested duration. Bear in mind that a lot of the value in these meetings comes from the discussions, so please be reasonable regarding the duration of the talk.

Important dates

The FOSDEM organisers hope to be able to live-stream and record all the talks. The recordings will be published under the same licence as all FOSDEM content (CC-BY). Only presentations will be recorded, not informal discussions and whatever happens during the lunch break. By agreeing to present at FOSDEM, you automatically give permission to be recorded. The organisers will agree to make exceptions but only for exceptional and well-reasoned cases.

Mailing list

Feel free to subscribe to the mailing list of the EDA devroom to submit ideas, ask questions and generally discuss about the event.

Please submit your proposals at https://penta.fosdem.org/submission/FOSDEM15 before 1 December 2014.

If you already have a Pentabarf account (for example as a result of having submitted a proposal in the past), make sure you use it to log in and submit your proposal. Do not create a new account if you already have one. Please provide a bit of information about yourself in Person -> Biography. When you submit your proposal (creating an "Event" in Pentabarf), make sure you choose the "Electronic design automation devroom" in the track drop-down menu. Otherwise your proposal might go unnoticed. Fill in at least a title and abstract for the proposed talk and a suggested duration. Bear in mind that a lot of the value in these meetings comes from the discussions, so please be reasonable regarding the duration of the talk.

Important dates

- 1 December 2014: deadline for submission of proposals

- 15 December 2014: speakers notified

- 30 December 2014: schedule published at https://fosdem.org/

- 1 February 2015: devroom day

The FOSDEM organisers hope to be able to live-stream and record all the talks. The recordings will be published under the same licence as all FOSDEM content (CC-BY). Only presentations will be recorded, not informal discussions and whatever happens during the lunch break. By agreeing to present at FOSDEM, you automatically give permission to be recorded. The organisers will agree to make exceptions but only for exceptional and well-reasoned cases.

Mailing list

Feel free to subscribe to the mailing list of the EDA devroom to submit ideas, ask questions and generally discuss about the event.

Spread the word!

This is the first EDA devroom at FOSDEM. Let's make sure as many projects and developers as possible are present. Thanks!

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To unsubscribe from this group and stop receiving emails from it, send an email to mos-ak+unsubscribe@googlegroups.com.

To post to this group, send email to mos-ak@googlegroups.com.

Visit this group at http://groups.google.com/group/mos-ak.

For more options, visit https://groups.google.com/d/optout.

Nov 18, 2014

[mos-ak] [Final Program] 7th International MOS-AK Workshop; December 12, 2014 at Berkeley

7th International MOS-AK Workshop

Berkeley Friday, Dec. 12, 2014

Final Program

Together with the MOS-AK Workshop Scientific Program Coordinators Larry Nagel and Andrei Vladimirescu as well as Extended MOS-AK TPC Committee, we have pleasure to invite to the 7th consecutive International MOS-AK Workshop which will be held at Berkeley, California, USA. The event is organized with aims to strengthen a network and discussion forum among experts in the field, enhance open platform for information exchange related to compact/Spice modeling and Verilog-A standardization, bring people in the compact modeling field together, as well as obtain feedback from technology developers, circuit designers, and CAD/EDA tool vendors.

Venue:

Room 540 in Cory HallEECS DepartmentUniversity of California, Berkeley

http://www.mos-ak.org/berkeley_2014/

Free on-line workshop registration:

http://www.mos-ak.org/berkeley_2014/registration.php

Postworkshop publications:

Selected best MOS-AK technical presentation will be recommended for further publication in a special issue of the International Journal of High Speed Electronics and Systems

Extended MOS-AK/GSA Committee

http://www.mos-ak.org/

Postworkshop publications:

Selected best MOS-AK technical presentation will be recommended for further publication in a special issue of the International Journal of High Speed Electronics and Systems

Extended MOS-AK/GSA Committee

WG181114

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To unsubscribe from this group and stop receiving emails from it, send an email to mos-ak+unsubscribe@googlegroups.com.

To post to this group, send email to mos-ak@googlegroups.com.

Visit this group at http://groups.google.com/group/mos-ak.

For more options, visit https://groups.google.com/d/optout.

Nov 16, 2014

NEW BOOK - Fabless: The Transformation of the Semiconductor Industry

Fabless: The Transformation of the Semiconductor Industry

By Daniel Nenni and Paul McLellan

Foreword By TSMC

The purpose of this book is to illustrate the magnificence of the fabless semiconductor ecosystem, and to give credit where credit is due by tracing the history of the semiconductor industry from both a technical and business perspective. [Book Preview]

Coupon code: LinkedIn2014

The author is offering to all LinkedIn connections a 50% off coupon code for the eBook version of "Fabless: The Transformation of the Semiconductor Industry". Feel free to forward this info to a friend or coworker. This eBook coupon expires on December 31, 2014. A paper version of the book is available on Amazon. For either version please click HERE for the SemiWiki shopping cart.

[mos-ak] Public release of MAPP at coming MOS-AK Meeting in Berkeley on Dec.12

Join the NEEDS Group in Berkeley on Dec. 12 for the MOS-AK Meeting for the public release of MAPP: the NEEDS Matlab-based Model Analysis and Prototyping Platform.

-- read more:

- 7th International MOS-AK Compact Modeling Workshop

- nanohub.org: NEEDS Nano-Engineered Electronic Device Simulation Node

- Get Started On Compact Modeling by Colin McAndrew at Purdue for the Nov. 18-19 Workshop.

- Newest NEEDS compact model releases

- MOS-AK Open Compact Modeling Directory

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To unsubscribe from this group and stop receiving emails from it, send an email to mos-ak+unsubscribe@googlegroups.com.

To post to this group, send email to mos-ak@googlegroups.com.

Visit this group at http://groups.google.com/group/mos-ak.

For more options, visit https://groups.google.com/d/optout.

Nov 13, 2014

Yannis Tsividis' Early Contributions to MOS Filters

In the 1970s, when the bipolar transistor was the undisputed king of analog integrated circuits (ICs), most electrical engineers regarded the MOS transistor as a second-rate device for ICs: it was a good switch, but a mediocre amplifier. As a graduate student at UC Berkeley, under the supervision of Paul Gray, Yannis Tsividis had a very different vision. He saw the MOS transistor as the future star for mixed-signal ICs and was excited to prove to the world he was right. The opening gambit was his thesis work demonstrating the first fully-integrated MOS opamp. This single achievement propelled him to the top of his generation of researchers and earned him a Berkeley PhD degree, a teaching appointment at Columbia University and a consulting position at Bell Laboratories.

[read more...]

REF:

Khoury, J.; Banu, M., "Yannis Tsividis' Early Contributions to MOS Filters," Solid-State Circuits Magazine, IEEE , vol.6, no.4, pp.36,40, Fall 2014

doi: 10.1109/MSSC.2014.2347772

Nov 10, 2014

i-MOS version 201410 release

New release of the interactive Modeling and On-line Simulation Platform (i-MOS), version 201410 has been released. In this release we have launched some new features:

- Developing an ‘Equalizer’ module in the ‘Model’ page for easy model parameter tuning

- Accommodating multiple parameters in this module for users’ most convenience

- Improving the ‘Custom data’ function for manual parameter extractions

- Updating the TFET model e-TIM (previous e-TuT) to support multiple materials

- Including an am-bipolar current module in the e-TIM

Location:

Hong Kong

Nov 4, 2014

IEEE Swiss CAS/ED Workshop 2014 on Memristive Devices and Neuromorphic Applications

IEEE Swiss CAS/ED Workshop 2014 on Memristive Devices and Neuromorphic Applications

(http://www.ieee.ch/chapters/cas-ed/cas-ed-news/2014-11-27/)

Date: Friday 28 Nov, 2014

Time: 10:00-19:00

Place: UZH, Irchel Campus, Room Y35 F51 (morning session) Y10 03/04 (afternoon session), Building 55 Foyer (apero). Closest tram stop is Tram 9/10 at Irchel. See here for University of Zurich map.

At this one day workshop, experts in Memristive Devices and Neuromorphic Applications will present their recent advances in Circuits and Systems and Electron Devices. The workshop includes a demo and poster session, and a concluding apero.

Resistive memory devices also known as "memristors" are being actively researched to address the widening gap in performance between storage and the rest of the computing system. There is also a potential for such devices to serve simultaneously as both memory and logic, or even as components of a neuromorphic computing hardware based on brain architecture. The investigation of the use of these devices in a host of applications in science and technology are currently being explored. Swiss developers are very active in these fields and the area of neuromorphic computing. This one-day IEEE workshop brings them together with potential research and development partners and end users in industry and academia.

The presentations will cover a range of topics focus on memristive technology and possible computing applications. A poster session including demonstrations of relevant technologies will also be offered.

All presentations will be in English.

Registration: Registration is open to the public but is mandatory. There will be a registration fee which includes lunch and apero. Please register at www.iniforum.ch/casedws14/registration.php.

Registration will be closed by 14.11.2014 or when the maximum number of places is reached. Registration must be cancelled by 21.11.2014 for refund.

Posters and Demos registration: We invite demos and posters. Poster or demo presentations must also register for the workshop (see above). Posters or demos must be registered so that we can plan space for them. Please use this demo and registration form to register.

Labels:

EDS,

IEEE,

memristors,

workshop

Location:

Zurich, Switzerland

Oct 26, 2014

EDS VLSI Technology and Circuits TC Report

EDS VLSI Technology and Circuits Technical Committee Report

The VLSI Technology and Circuits Technical Committee was formed in 1998 under the leadership of Professor Charles G. Sodini (MIT) and followed by Dr. H.-S. Philip Wong (IBM), Werner Weber (Infineon), Dr. James A. Hutchby (SRC) and Dr. Bin Zhao (Freescale Semiconductor). Since its formation, the VLSI Committee has made it their mission to identify new technical trends, help foster new technical concepts, and serve the emerging needs of the Electron Devices and Solid-State Circuits communities in VLSI. The committee members include many well recognized technical experts representing a very wide spectrum of technical expertise in VLSI devices, technology, and circuits. Every year the committee brainstorms (by email), ideas that are suitable for new workshops, special issues for a journals, panel sessions, and special sessions for conferences. Committee members then drive these ideas forward and find a way to make them happen; either by being the organizers themselves, or by finding suitable organizers for the topic. They work closely together with journal editors and conference organizers. It is much easier to attach new workshops to existing conferences, than to establish new conferences.

[read more at http://eds.ieee.org/eds-newsletters.html]

Oct 24, 2014

IEEE TED Call for Papers: Variation aware technology and circuit codesign

Call for papers for a special issue of

IEEE Transactions on Electron Devices

"Variation aware technology and circuit codesign"

The special issue on "variation aware technology and circuit co design is devoted to the research and development activities on variation aware process device technology and co-optimization with circuit design. Rapid pace of new technology introduction to CMOS technology requires much more sophisticate optimization of process, device, and circuit design, in order to maximize return on investment. Careful optimization of process technology, device structure, layout and circuit design in holistic manner enables significant performance improvement while reducing overall power consumption with least amount of area penalty.

Among many challenges for this holistic optimization, higher process and device variation becomes one of most critical issues as process technology is marching into below 20nm node.

New material technology and non-planar device structure add additional variation source on top of conventional geometrical effect. Not only reducing extrinsic portion of variation is important understanding the effect of such variation in various actual circuit design is also very important In addition to addressing variation at individual process and design element, this special edition also touches on the impact of variation aware optimization to overall SOC design that requires both high performance and low power functional blocks.

This special edition includes, but not limited to, following topics:

- Variation reduction methods of advanced process technology, including patterning, deposition and etch processes

- Variation reduction methods of dvanced device technology, including FinFET, Nanowire, FDSOL etc.

- Co-optimization of technology and circuit to minimize variation and/orimpact of variation.

- ТCAD to understand the source of variation and provide practical method to improve.

- Novel process and device technology to cope with variation issue in coming nodes.

- SOC integration and design methodology to take process device variation into account.

BE SURE TO MENTION THE SPECIAL ISSUE WITHIN THE COVER LETTER

Submission Deadline: October 31, 2014

Scheduled Publication Date: June 2015

Guest Editors:

Stanley S.C. Song Qualcomm

Huiling Shang, IBM

Каustav Banerjee, University of California, Santa Barbara

Shuji Ikeda, TEI solution

If you have any questions about submitting a manuscript, please contact:

Jo Ann Marsh (j.marsh@ieee.org) T-ED Special Issues Administrative Support

Oct 15, 2014

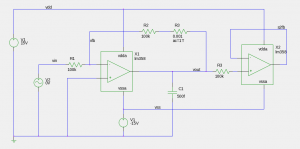

AC and Stability Analysis in NGSPICE

The above example shows an AC analysis test-bench GSCHEM. In this example the loop is broken by R3 whose value at dc is 1mO and is changed to 1TO for ac analysis. Doing this enables NGSPICE to converge on a sensible dc operating point for open loop analysis without any imperfections such as input offset forcing the output to one of the supply rails. [read more at http://education.ingenazure.com/]

Oct 13, 2014

Wearable Sensing and Computing

Wearable Sensing and Computing

05.11.2014 - 06.11.2014

EPFL Lausanne (CH)

COURSE OBJECTIVES

The course main objective is to inform and discuss in great details the latest advancements in low power sensing technology, energy harvesting and their heterogeneous integration for wearable smart system applications. Technological roadmaps of performance and future evolutions will be presented. The low power wireless communications are discussed from the point of view of existing standards and challenges for reducing the energy per communicated bit. Another objective is to detail some key future applications for wearable sensing and computing with main emphasis on: (1) medical Diagnostics, monitoring and prevention and (2) sports, fitness and activity monitoring applications. We analyze the benefits of autonomous smart system technology from many different points of view, including that of the individual, the physician, health care management, and society in general. We provide a rationale on the role of such technology as a component of the care cycle and the changes it can induce by reinforcing preventive strategies.

AGENDA on-line

Day 1 (09:00 – 17:00):

- Introduction to wearable technology and energy efficient functions for autonomous smart systems

- Energy efficient computing technologies and their importance for wearable applications:

- Wearable low power sensor technology trends

- Wearable low power communications technologies

- Wearable energy harvesting technology trends

Day 2 (09:00 – 17:00):

- Heterogeneous integration: solutions, roadmaps and trends for wearables

- Context-driven embodiments by wearable systems and related applications and services

- Market Trends for Mobile and Wearable Technology

- Wearable autonomous smart systems: Applications to Medical Diagnostics, Monitoring and Prevention Paradigms using Feedback Loops

- Wearable Technology – Sports, Fitness and Activity Monitoring Applications

Course registration on-line

Labels:

Computing,

Training Courses,

Wearable Sensing

Location:

Lausanne, Switzerland

Oct 7, 2014

[mos-ak] 7th International MOS-AK Workshop; December 12, 2014 at Berkeley

7th International MOS-AK Workshop

Berkeley Friday, Dec. 12, 2014

Announcement and Call for Papers

Together with the MOS-AK Workshop Scientific Program Coordinators Larry Nagel and Andrei Vladimirescu as well as Extended MOS-AK TPC Committee, we have pleasure to invite to the 7th consecutive International MOS-AK Workshop which will be held at Berkeley, California, USA, in the IEDM Conference and CMC Meeting timeframe. The event is organized with aims to strengthen a network and discussion forum among experts in the field, enhance open platform for information exchange related to compact/Spice modeling and Verilog-A standardization, bring people in the compact modeling field together, as well as obtain feedback from technology developers, circuit designers, and CAD/EDA tool vendors.

Venue:

Room 540 in Cory HallEECS DepartmentUniversity of California, Berkeley

Important Dates:

Call for Papers - September 20142nd Announcement - October 2014Final Workshop Program - November. 2014MOS-AK Workshop - Friday, Dec. 12, 201408:30 - 09:00 - On-site Registration09:00 - 11:00 - Morning MOS-AK Session11:00 - 12:00 - CM Standardization Panel12:00 - 13:00 - Lunch13:00 - 16:00 - Afternoon MOS-AK Session

- Advances in semiconductor technologies and processing

- Compact Modeling (CM) of the electron devices

- Verilog-A language for CM standardization

- New CM techniques and extraction software

- Open Source TCAD/EDA modeling and simulation

- CM of passive, active, sensors and actuators

- Emerging Devices, CMOS and SOI-based memory cells

- Microwave, RF device modeling, high voltage device modeling

- Nanoscale CMOS devices and circuits

- Technology R&D, DFY, DFT and IC Designs

- Foundry/Fabless Interface Strategies

Authors should submit an abstract using on-line MOS-AK submission form (any related inquiries can be sent to abstracts@mos-ak.org)

http://www.mos-ak.org/berkeley_2014/abstracts.php

On-line free workshop registration:

http://www.mos-ak.org/berkeley_2014/registration.php

Postworkshop publications:

Selected best MOS-AK technical presentation will be recommended for further publication in a special issue of the International Journal of High Speed Electronics and Systems

Extended MOS-AK/GSA Committee

WG06102014

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To unsubscribe from this group and stop receiving emails from it, send an email to mos-ak+unsubscribe@googlegroups.com.

To post to this group, send email to mos-ak@googlegroups.com.

Visit this group at http://groups.google.com/group/mos-ak.

For more options, visit https://groups.google.com/d/optout.

Subscribe to:

Posts (Atom)