Mikhail Basov

Pressure sensor chip utilizing electrical circuit of piezosensitive differential amplifier with negative feedback loop (PDA-NFL) for 5 kPa

XI International Scientific and Technical Conference

"Micro-, and Nanotechnology in Electronics",

Elbrus, Russia; June 2021

Dukhov Automatics Research Institute VNIIA, Moscow

Abstract: High sensitive (S=11.2±1.8 mV/V/kPa with nonlinearity error 2KNL=0.15±0.09 % /FS) small-sized (4.00x4.00 mm2) silicon pressure sensor chip utilizing new electrical circuit for microelectromechanical systems (MEMS) in the form of differential amplifier with negative feedback loop (PDA-NFL) for 5 kPa differential was developed. The advantages are demonstrated in the array of output characteristics, which prove the relevance of the presented development, relative to modern developments of pressure sensors with Wheatstone bridge electrical circuit for 5 kPa range.

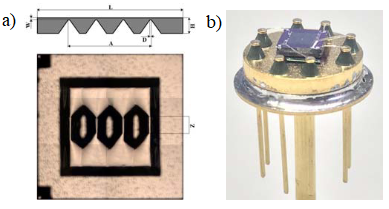

Fig: a) Pressure sensor chip, b) its assembled structure