High spatial resolution monolithic pixel detector in SOI technology

R. Bugiela1, S. Bugiela2, D. Dannheimb, A. Fiergolskib, D. Hyndsb,3, M. Idzika, P. Kapustac, M. Munkerb, A. Nurnbergb4, S. Spannagelb,5, K. Swienteka, W. Kucewicza

aAGH-UST, Poland, bCERN, Switzerland, cIFJ PAN, Poland

CLICdp-Pub-2020-004

06 August 2020

1Present: CNRS/IPHC, France.

2Present: CNRS/IPHC, France.

3Present: NIKHEF, Amsterdam, Netherlands.

4Present: KIT, Karlsruhe, Germany.

5Present: DESY, Hamburg, Germany.

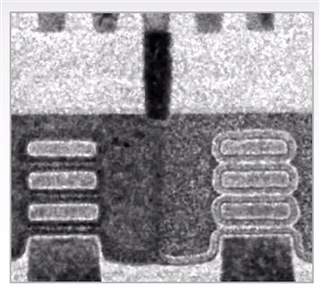

Abstract: This paper presents test-beam results of monolithic pixel detector prototypes fabricated in 200nm Silicon-On-Insulator (SOI) CMOS technology studied in the context of high spatial resolution performance. The tested detectors were fabricated on a 500µm thick highresistivity Floating Zone type n (FZ-n) wafer and on a 300 µm Double SOI Czochralski type p (DSOI Cz-p) wafer. The pixel size is 30µm×30µm and two different front-end electronics architectures were tested, a source follower and a charge-sensitive preamplifier. The test-beam data analyses were focused mainly on determination of the spatial resolution and the hit detection efficiency. In this work different cluster formation and position reconstruction methods are studied. In particular, a generalization of the standard η-correction adapted for arbitrary cluster sizes, is introduced. The obtained results give in the best case a spatial resolution of about 1.5µm for the FZ-n wafer and about 3.0µm for the DSOI Cz-p wafer, both detectors showing detection efficiency above 99.5%.

Fig.: Simplified schematics of Silicon-On-Insulator structures. The Buried N(P)-Well (BN(P)W) is a layer dedicated to shielding the electronics from the sensors electric field.

Aknowlegement: This work was financed by the European Union Horizon 2020 Marie Sklodowska-Curie Research and Innovation Staff Exchange program under Grant Agreement no. 645479 (E-JADE) and also by the Polish Ministry of Science and Higher Education from funds for science in the years 2017 – 2018 allocated to an international co-financed project. The authors would like to thank also the operators of the CERN SPS beam line and North Area test facilities.

Rajiv V. Joshi

Rajiv V. Joshi