Characterization and Modeling of 0.18µm Bulk CMOS Technology

at Sub-Kelvin Temperature

Teng-Teng Lu1,2, Zhen Li1,2, Chao Luo1,2, Jun Xu2, Weicheng Kong3,

and Guoping Guo1 (Member, IEEE)

IEEE J-EDS, vol. 8, pp. 897-904, 2020

DOI: 10.1109/JEDS.2020.3015265.

1Key Laboratory of Quantum Information, University of Science and Technology of China, Hefei 230026, China

2Department of Physics, University of Science and Technology of China, Hefei 230026, China

3Department of Quantum Hardware, Origin Quantum Computing Company Limited, Hefei 230026, China

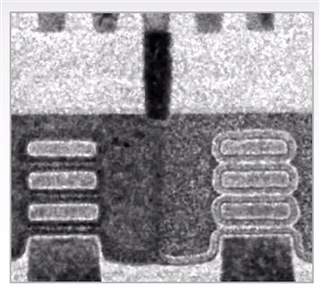

Abstract: Previous cryogenic electronics studies are mostly at 77K and 4.2K. Cryogenic characterization of a 0.18μm standard bulk CMOS technology (operating voltages: 1.8V and 5V) is presented in this paper. Several NMOS and PMOS devices with different width to length ratios (W/L) were extensively tested and characterized under various bias conditions at sub-kelvin temperature. In addition to devices dc characteristics, the kink effect and current overshoot phenomenon are observed and discussed at sub-kelvin temperature. Especially, the current overshoot phenomenon in PMOS devices at sub-kelvin temperature is shown for the first time. The transfer characteristics of MOSFET devices (1.8V W/L = 10μm/10μm) at sub-kelvin temperature are modeled using the simplified EKV model. This work facilitates the CMOS circuits design and the integration of CMOS circuits with silicon-based quantum chips at extremely low temperatures.

FIG: IDS-VGS curves of large thin TOX NMOS (a,b,e,f) and PMOS (c,d,g,h) devices at sub-kelvin temperature measured (symbols) and simulated (solid lines).

Aknowlegement: This work was supported in part by the National Key Research and Development Program of China under Grant 2016YFA0301700, in part by the National Natural Science Foundation of China under Grant 11625419, in part by the Anhui initiative in Quantum information Technologies under Grant AHY080000, and in part by the USTC Center for Micro and Nanoscale Research and Fabrication.