*Semiconductor Technologies Research Laboratory, Tübitak Bilgem Yital, Kocaeli, Turkey

Jan 17, 2024

[paper] RF NMOS Transistor in a 0.25 µm SiGe-C BiCMOS Process

*Semiconductor Technologies Research Laboratory, Tübitak Bilgem Yital, Kocaeli, Turkey

Jan 15, 2024

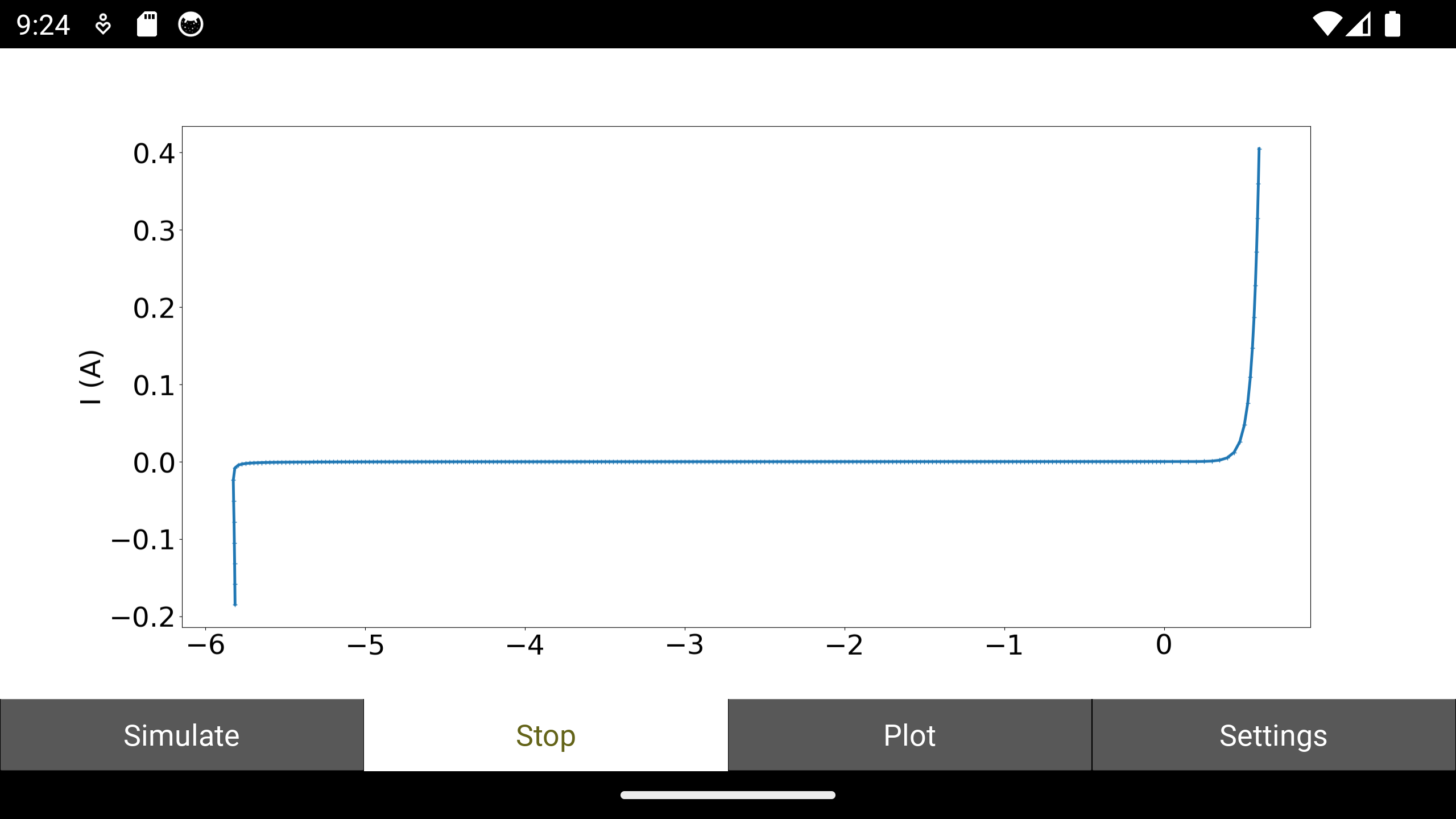

DEVSIM as TCAD mobile app

Now through January 18, 2024, the TCAD app is free for download. After this, you will be entitled to any free future updates [read more...]

- App is renamed to “TCAD app”

- Impact ionization model added

- Menus updated

- Easier plot navigation

- Series resistance available to aid in impact ionization model results

- Stop simulation and keep partial results to stop long-running simulation early

[C4P] MIXDES 2024

- Design of Integrated Circuits and Microsystems

Design methodologies. Digital and analog synthesis. Hardware-software co-design. Reconfigurable hardware. Hardware description languages. Intellectual property-based design. Design reuse. - Thermal Issues in Microelectronics

Thermal and electro-thermal modelling, simulation methods and tools. Thermal mapping. Thermal protection circuits. - Analysis and Modelling of ICs and Microsystems

Simulation methods and algorithms. Behavioral modelling with VHDL-AMS and other advanced modelling languages. Microsystems modelling. Model reduction. Parameter identification. - Microelectronics Technology and Packaging

New microelectronic technologies. Packaging. Sensors and actuators. - Testing and Reliability

Design for testability and manufacturability. Measurement instruments and techniques. - Power Electronics

Design, manufacturing, and simulation of power semiconductor devices. Hybrid and monolithic Smart Power circuits. Power integration. - Signal Processing

Digital and analogue filters, telecommunication circuits. Neural networks. Artificial intelligence. Fuzzy logic. Low voltage and low power solutions. - Embedded Systems

Design, verification and applications. - Medical Applications

Medical and biotechnology applications. Biometrics. Thermography in medicine

Tutorials and Special Sessions - Call for Proposals

Jan 11, 2024

[paper] Neural Compact Modeling Framework

Abstract: Neural compact models are proposed to simplify device-modeling processes without requiring domain expertise. However, the existing models have certain limitations. Specifically, some models are not parameterized, while others compromise accuracy and speed, which limits their usefulness in multi-device applications and reduces the quality of circuit simulations. To address these drawbacks, a neural compact modeling framework with a flexible selection of technology-based model parameters using a two-stage neural network (NN) architecture is proposed. The proposed neural compact model comprises two NN components: one utilizes model parameters to program the other, which can then describe the current–voltage (IV) characteristics of the device. Unlike previous neural compact models, this two-stage network structure enables high accuracy and fast simulation program with integrated circuit emphasis (SPICE) simulation without any trade-off. The IV characteristics of 1000 amorphous indium–gallium–zinc-oxide thin-film transistor devices with different properties obtained through fully calibrated technology computer-aided design simulations are utilized to train and test the model and a highly precise neural compact model with an average IDS error of 0.27% and R2 DC characteristic values above 0.995 is acquired. Moreover, the proposed framework outperforms the previous neural compact modeling methods in terms of SPICE simulation speed, training speed, and accuracy.

[github] new RevEDA Release

Any interested parties are kindly invited to get in touch with Murat Eskiyerli, the lead RevEDA developer