- Developing an ‘Equalizer’ module in the ‘Model’ page for easy model parameter tuning

- Accommodating multiple parameters in this module for users’ most convenience

- Improving the ‘Custom data’ function for manual parameter extractions

- Updating the TFET model e-TIM (previous e-TuT) to support multiple materials

- Including an am-bipolar current module in the e-TIM

Nov 10, 2014

i-MOS version 201410 release

New release of the interactive Modeling and On-line Simulation Platform (i-MOS), version 201410 has been released. In this release we have launched some new features:

Location:

Hong Kong

Nov 4, 2014

IEEE Swiss CAS/ED Workshop 2014 on Memristive Devices and Neuromorphic Applications

IEEE Swiss CAS/ED Workshop 2014 on Memristive Devices and Neuromorphic Applications

(http://www.ieee.ch/chapters/cas-ed/cas-ed-news/2014-11-27/)

Date: Friday 28 Nov, 2014

Time: 10:00-19:00

Place: UZH, Irchel Campus, Room Y35 F51 (morning session) Y10 03/04 (afternoon session), Building 55 Foyer (apero). Closest tram stop is Tram 9/10 at Irchel. See here for University of Zurich map.

At this one day workshop, experts in Memristive Devices and Neuromorphic Applications will present their recent advances in Circuits and Systems and Electron Devices. The workshop includes a demo and poster session, and a concluding apero.

Resistive memory devices also known as "memristors" are being actively researched to address the widening gap in performance between storage and the rest of the computing system. There is also a potential for such devices to serve simultaneously as both memory and logic, or even as components of a neuromorphic computing hardware based on brain architecture. The investigation of the use of these devices in a host of applications in science and technology are currently being explored. Swiss developers are very active in these fields and the area of neuromorphic computing. This one-day IEEE workshop brings them together with potential research and development partners and end users in industry and academia.

The presentations will cover a range of topics focus on memristive technology and possible computing applications. A poster session including demonstrations of relevant technologies will also be offered.

All presentations will be in English.

Registration: Registration is open to the public but is mandatory. There will be a registration fee which includes lunch and apero. Please register at www.iniforum.ch/casedws14/registration.php.

Registration will be closed by 14.11.2014 or when the maximum number of places is reached. Registration must be cancelled by 21.11.2014 for refund.

Posters and Demos registration: We invite demos and posters. Poster or demo presentations must also register for the workshop (see above). Posters or demos must be registered so that we can plan space for them. Please use this demo and registration form to register.

Labels:

EDS,

IEEE,

memristors,

workshop

Location:

Zurich, Switzerland

Oct 26, 2014

EDS VLSI Technology and Circuits TC Report

EDS VLSI Technology and Circuits Technical Committee Report

The VLSI Technology and Circuits Technical Committee was formed in 1998 under the leadership of Professor Charles G. Sodini (MIT) and followed by Dr. H.-S. Philip Wong (IBM), Werner Weber (Infineon), Dr. James A. Hutchby (SRC) and Dr. Bin Zhao (Freescale Semiconductor). Since its formation, the VLSI Committee has made it their mission to identify new technical trends, help foster new technical concepts, and serve the emerging needs of the Electron Devices and Solid-State Circuits communities in VLSI. The committee members include many well recognized technical experts representing a very wide spectrum of technical expertise in VLSI devices, technology, and circuits. Every year the committee brainstorms (by email), ideas that are suitable for new workshops, special issues for a journals, panel sessions, and special sessions for conferences. Committee members then drive these ideas forward and find a way to make them happen; either by being the organizers themselves, or by finding suitable organizers for the topic. They work closely together with journal editors and conference organizers. It is much easier to attach new workshops to existing conferences, than to establish new conferences.

[read more at http://eds.ieee.org/eds-newsletters.html]

Oct 24, 2014

IEEE TED Call for Papers: Variation aware technology and circuit codesign

Call for papers for a special issue of

IEEE Transactions on Electron Devices

"Variation aware technology and circuit codesign"

The special issue on "variation aware technology and circuit co design is devoted to the research and development activities on variation aware process device technology and co-optimization with circuit design. Rapid pace of new technology introduction to CMOS technology requires much more sophisticate optimization of process, device, and circuit design, in order to maximize return on investment. Careful optimization of process technology, device structure, layout and circuit design in holistic manner enables significant performance improvement while reducing overall power consumption with least amount of area penalty.

Among many challenges for this holistic optimization, higher process and device variation becomes one of most critical issues as process technology is marching into below 20nm node.

New material technology and non-planar device structure add additional variation source on top of conventional geometrical effect. Not only reducing extrinsic portion of variation is important understanding the effect of such variation in various actual circuit design is also very important In addition to addressing variation at individual process and design element, this special edition also touches on the impact of variation aware optimization to overall SOC design that requires both high performance and low power functional blocks.

This special edition includes, but not limited to, following topics:

- Variation reduction methods of advanced process technology, including patterning, deposition and etch processes

- Variation reduction methods of dvanced device technology, including FinFET, Nanowire, FDSOL etc.

- Co-optimization of technology and circuit to minimize variation and/orimpact of variation.

- ТCAD to understand the source of variation and provide practical method to improve.

- Novel process and device technology to cope with variation issue in coming nodes.

- SOC integration and design methodology to take process device variation into account.

BE SURE TO MENTION THE SPECIAL ISSUE WITHIN THE COVER LETTER

Submission Deadline: October 31, 2014

Scheduled Publication Date: June 2015

Guest Editors:

Stanley S.C. Song Qualcomm

Huiling Shang, IBM

Каustav Banerjee, University of California, Santa Barbara

Shuji Ikeda, TEI solution

If you have any questions about submitting a manuscript, please contact:

Jo Ann Marsh (j.marsh@ieee.org) T-ED Special Issues Administrative Support

Labels:

call for papers,

IEEE,

TED

Oct 15, 2014

AC and Stability Analysis in NGSPICE

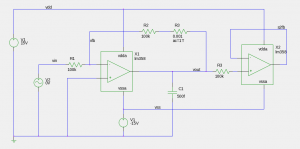

The above example shows an AC analysis test-bench GSCHEM. In this example the loop is broken by R3 whose value at dc is 1mO and is changed to 1TO for ac analysis. Doing this enables NGSPICE to converge on a sensible dc operating point for open loop analysis without any imperfections such as input offset forcing the output to one of the supply rails. [read more at http://education.ingenazure.com/]

Subscribe to:

Comments (Atom)