The IEEE EDS Delhi Chapter, New Delhi, India is conducting a series of the IEEE EDS DL Talks with coming one on June 03, 2020 at 06:00 pm (GMT+05:30, IST) with following topic:

FOSS TCAD/EDA tools for Compact/SPICE Modeling

Wladek Grabinski

Senior Member-IEEE MOS-AK Association (EU)

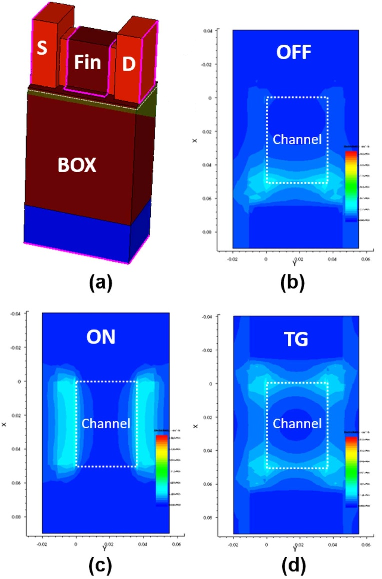

Abstract: Compact/SPICE models of circuit elements (passive, active, MEMS, RF) are essential to enable advanced IC design using nanoscaled semiconductor technologies. Compact/SPICE models are also a communication means between the semiconductor foundries and the IC design teams to share and exchange all engineering and design information. To explore all related interactions, we are discussing selected FOSS CAD tools along complete technology/design tool chain from nanascaled technology processes; thru the MOSFET, FDSOI, FinFET and TFET compact modeling; to advanced IC transistor level design support. New technology and device development will be illustrated by application examples of the FOSS TCAD tools: Cogenda TCAD and DEVSIM. Compact modeling will be highlighted by review topics related to its parameter extraction and standardization of the experimental and measurement data exchange formats. Finally, we will present two FOSS CAD simulation and design tools: ngspice and Qucs. Application and use of these tools for advanced IC design (e.g. analog/RF IC applications) directly depends on the quality of the compact models implementations in these tools as well as reliability of extracted models and generated libraries/PDKs. Discussing new model implementation into the FOSS CAD tools (Gnucap, Xyce, ngspice and Qucs as well as others) we will also address an open question of the compact/SPICE model Verilog-A standardization. We hope that this presentation will be useful to all the researchers and engineers actively involved in the developing compact/SPICE models as well as designing the integrated circuits in particular at the transistor level and then trigger further discussion on the compact/SPICE model Verilog-A standardization to encourage development FOSS CAD tools.

The series of the IEEE EDS DLs are coordinated by:

Professor Mridula Gupta

Chairperson-IEEE EDS Delhi ChapterProfessor & Head of Department of Electronic ScienceUniversity of Delhi South CampusNew Delhi 110021INDIA

Professor Manoj Saxena

Regional Editor for South Asia, IEEE EDS NewsletterEDS Distinguished Lecturer and Fellow-IETE, IndiaAssociate Professor, Department of ElectronicsDeen Dayal Upadhyaya College, University of DelhiDwarka Sector-3, New Delhi-110078, India