Neha Parasa, Shiromani Balmukund Rahib, Abhishek Kumar Upadhyayc,

Manisha Bhartid, Young Suh Songe

Design and analysis of novel La:HfO2 gate stacked ferroelectric tunnel FET

for non-volatile memory applications

Memories - Materials, Devices, Circuits and Systems

Volume 7, April 2024, 100101

DOI: 10.1016/j.memori.2024.100101

a Jawaharlal Nehru University, New Delhi, India

b Indian Institute of Technology, Kanpur, India

c X-FAB Dresden GmbH & Co. KG, Dresden, Germany

d National Institute of Technology, Delhi, India

e Korea Military Academy, Seoul, Republic of Korea

Abstract

: Recent experimental studies have shown lanthanum-doped hafnium oxide (La:HfO2) possessing ferroelectric properties. This material is of special interest since it is based on lead-free, simple binary oxide of HfO2, and has excellent endurance property (1 × 109 field cycles without fatigue. There exists substantial information about the material aspects of La:HfO2 but it lacks proven application potential for CMOS-compatible low-power memory design. In this work, 10 % La metal cation fraction of HfO2 (La:HfO2) is proposed as the gate stack material in tunnel FET (TFET) for its potential as a memory device. 2D device simulations are carried out to show that the proposed ferroelectric TFET (FeTFET) provides the largest memory window (MW) as compared to present perovskite ferroelectric materials such as PZT, SBT (SrBi2Ta2O9) and silicon doped (4.6 % Si in HfO2) hafnium oxide (Si:HfO2). The larger window is attributed to greater polarization, and the calculation of MW is quantified by the shift in threshold voltage (Vth). The simulations carried out in this work suggest that La:HfO2 can be adopted as a potential ferroelectric material to target low-power FeTFET design at significantly reduced ferroelectric layer thickness.

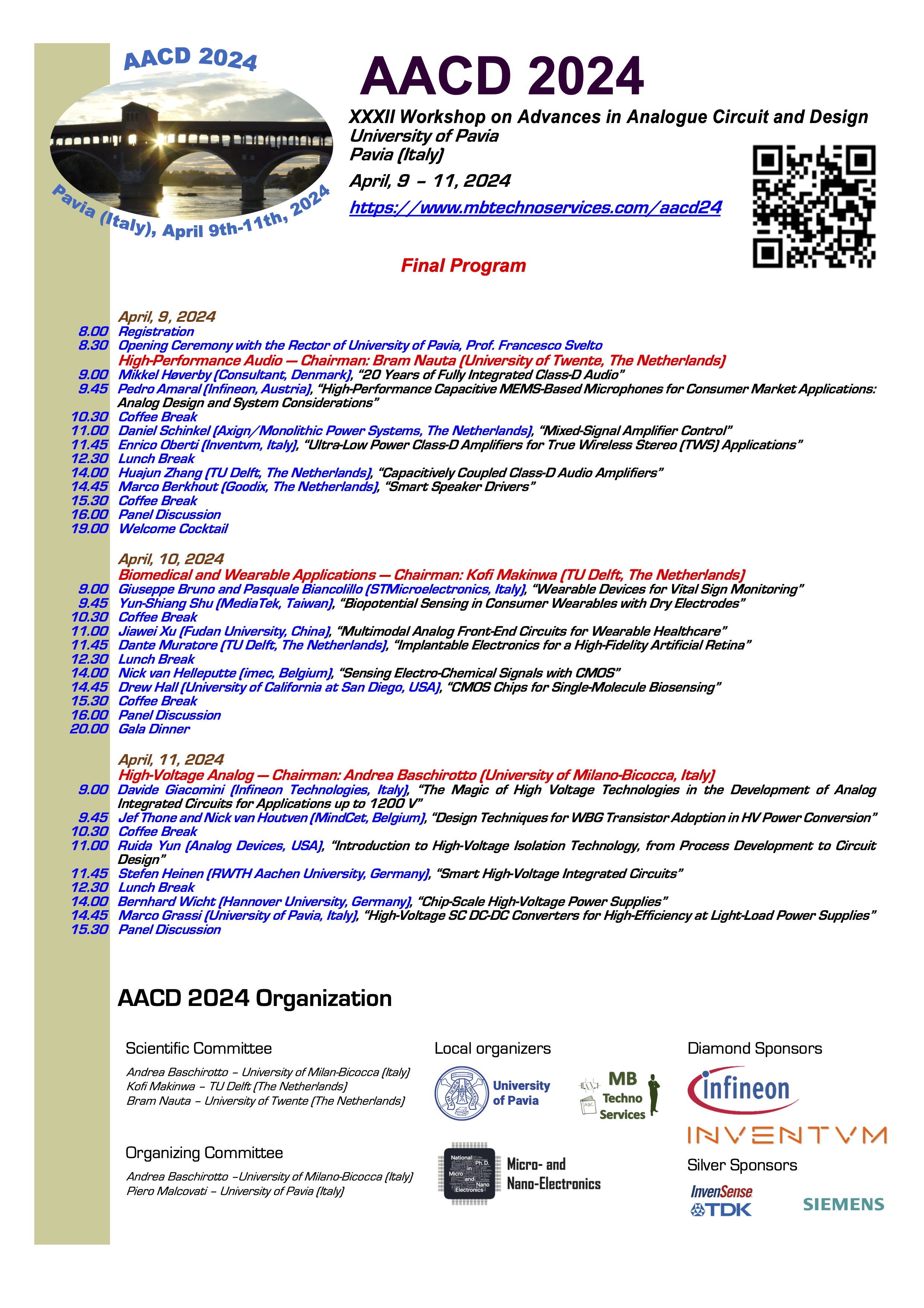

FIG: Polarization phenomena of the proposed

La:HfO2 gate stacked ferroelectric tunnel FET