Wang, Chien-Ping, Yi-Pei Tsai, Burn Jeng Lin, Zheng-Yong Liang, Po-Wen Chiu, Jiaw-Ren Shih, Chrong Jung Lin, and Ya-Chin King

On-Wafer FinFET-Based EUV/eBeam Detector Arrays for Advanced Lithography Processes

IEEE TED (2020)

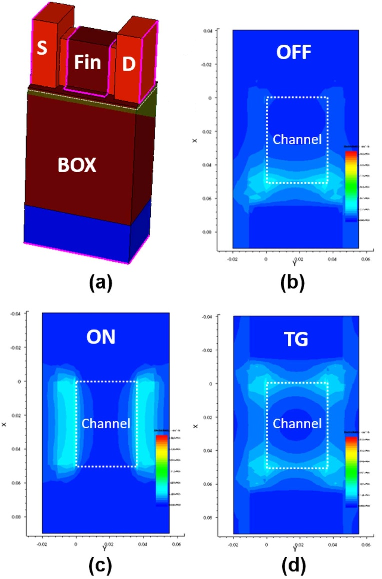

Abstract: A novel microdetector array (MDA) for monitoring electron beam (eBeam) and extreme ultraviolet (EUV) lithography processes in 5 nm and beyond FinFET technology is first-time presented. This on-wafer detector array consists of high-density sensing cells which are fully compatible with standard FinFET CMOS processes. Fin coupling structures and energy-sensing pads are first applied in an ultrasmall detector for realizing efficient eBeam and EUV photon detection. In advanced lithography process, eBeam or EUV level projected on the wafer can be precisely recorded on the on-wafer MDA without power or batteries. The distributions and variations on the beam intensities collected by MDA can be electrically measured in real time or inline through wafer level test after eBeam or EUV exposures. The proposed MDA is expected to provide real-time feedback for the optimization and stable maintenance of advanced photolithography processed critical to the development nanometer CMOS technologies.

FIG: (a) Schematic of lithography system and (b) 3-D illustration of unit detector cell of the MDA consisting of ESP and FG on the shallow trench isolation (STI) region.

Acknowledgment: The authors gratefully acknowledge the contributions of Taiwan Semiconductor Manufacturing Company (TSMC) and Ministry of Science and Technology (MOST), Taiwan (Project Number: MOST 108-2622-8-007-017).