#EU Parliament Strongly Recommends Developing and Using #opensource Software https://t.co/6HxdUaUHQK pic.twitter.com/7czSKFmwh7

— Wladek Grabinski (@wladek60) May 19, 2020

from Twitter https://twitter.com/wladek60

May 19, 2020 at 10:00AM

via IFTTT

#EU Parliament Strongly Recommends Developing and Using #opensource Software https://t.co/6HxdUaUHQK pic.twitter.com/7czSKFmwh7

— Wladek Grabinski (@wladek60) May 19, 2020

|

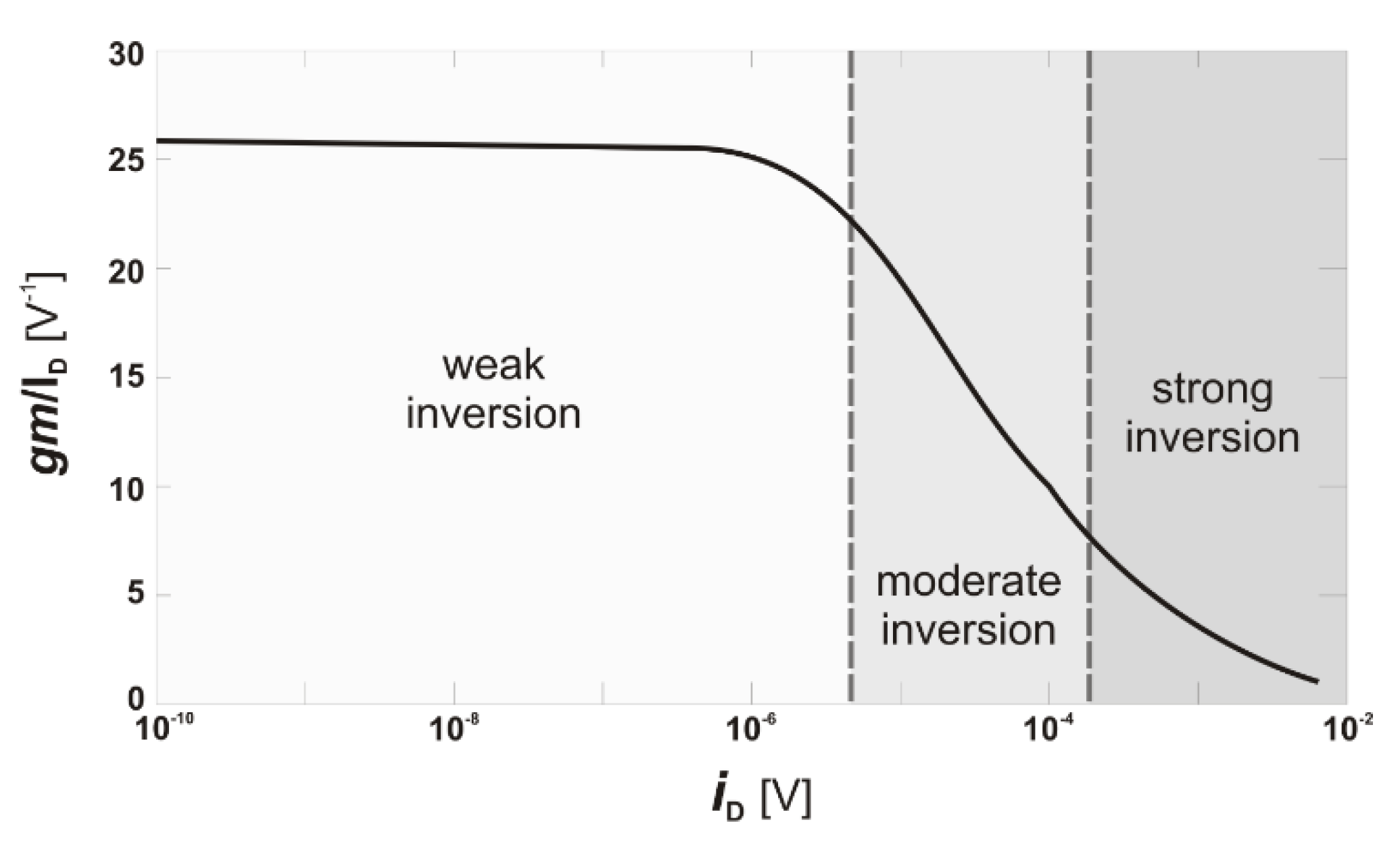

| Figure: gm/ID versus iD |

#Linux not #Windows: Why #Munich is shifting back from Microsoft to #opensource ...again https://t.co/7kCWSVHIOk pic.twitter.com/KVPAvUZr8o

— Wladek Grabinski (@wladek60) May 14, 2020

#paper: Smith, A.F., Liu, X., Woodard, T.L. et al. #Bioelectronic protein nanowire sensors for ammonia detection. Nano Res. (2020)https://t.co/eTvrtblGS0

— Wladek Grabinski (@wladek60) May 14, 2020

A new, highly sensitive #chemical #sensor uses protein nanowires https://t.co/lj2MoELcLp pic.twitter.com/03cHA6MNIc