#Microsoft readies #exFAT patents for #Linux and #opensource | ZDNet https://t.co/nGURHD35IU pic.twitter.com/NWBfJOiOyL

— Wladek Grabinski (@wladek60) August 29, 2019

from Twitter https://twitter.com/wladek60

August 29, 2019 at 11:11AM

via IFTTT

#Microsoft readies #exFAT patents for #Linux and #opensource | ZDNet https://t.co/nGURHD35IU pic.twitter.com/NWBfJOiOyL

— Wladek Grabinski (@wladek60) August 29, 2019

#IBM’s #OpenSource POWER Play: A #RISC-V Business? https://t.co/11lFmDgnpU pic.twitter.com/io81PcbNqh

— Wladek Grabinski (@wladek60) August 28, 2019

F. Ávila Herrera et al., "Advanced Short-Channel-Effect Modeling With Applicability to Device Optimization—Potentials and Scaling," in IEEE Transactions on Electron Devices, vol. 66, no. 9, pp. 3726-3733, Sept. 2019 https://t.co/6vkIpdH9F6 #paper pic.twitter.com/sVWISPjNKN

— Wladek Grabinski (@wladek60) August 28, 2019

3rd International Workshop on MEMS and Sensor System 2019 (#IWMS 2019) Aug. 27-29 Hi Chi Minh City (VN) https://t.co/hOnegKRO5E #paper pic.twitter.com/fPmyokXQ5w

— Wladek Grabinski (@wladek60) August 27, 2019

Is the Threat of ‘Fake Science’ Real?

— Wladek Grabinski (@wladek60) August 27, 2019

"Thinking ahead to the potential for fake science can better equip research institutions to respond to targeted disinformation while preserving an open scientific community."https://t.co/nzAokiqybW #paper pic.twitter.com/D0WasFZRwv

Y. Yamamoto et al., "The Study of Plasma Induced Damage on 65-nm Silicon on Thin BOX Transistor," in IEEE Journal of the Electron Devices Society, vol. 7, pp. 825-828, 2019https://t.co/ppz92LZnNi #paper pic.twitter.com/7hmMCY5rvx

— Wladek Grabinski (@wladek60) August 27, 2019

B. K. Esfeh, V. Kilchytska, N. Planes, M. Haond, D. Flandre and J. Raskin, "28-nm FDSOI nMOSFET RF Figures of Merits and Parasitic Elements Extraction at Cryogenic Temperature Down to 77 K," in IEEE JEDS, vol. 7, pp. 810-816, 2019.

— Wladek Grabinski (@wladek60) August 27, 2019

https://t.co/VXOuHjBAWI #paper pic.twitter.com/mT1vV0psze

低频噪声测试在新兴半导体材料和器件物理机制探索的应用研究

— Wladek Grabinski (@wladek60) August 27, 2019

Application Research of Low Frequency Noise Testing in the Exploration of Emerging Semiconductor Materials and Devices Physical Mechanismhttps://t.co/Y9lDjd1kPn #paper pic.twitter.com/6X4218ejOF

V. Veliadis, "The Impact of Education in Accelerating Commercialization of Wide-Bandgap Power Electronics [Expert View]," in IEEE Power Electronics Magazine, vol. 6, no. 2, pp. 62-66, June 2019

— Wladek Grabinski (@wladek60) August 26, 2019

doi: 10.1109/MPEL.2019.2910715 https://t.co/R14V6BDxXR #paper pic.twitter.com/NnTfIqzaRR

IEEE Annual Election: IEEE President-Elect Candidate: DEJAN S. MILOJICIC, PhD https://t.co/YGXMj7XzQM (Nominated by IEEE Board of Directors) Distinguished Technologist; Hewlett Packard Labs Palo Alto, California, USA

— Wladek Grabinski (@wladek60) August 26, 2019

https://t.co/eCpVS4yzu9 #paper pic.twitter.com/4b8EOTaQMF

B. Contreras, G. Ducoudray, R. Palomera and C. Bernal, "Automated Parameter Extraction and #SPICE #Model Modification For Gate Enclosed MOSFETs Simulation," 16th SMACD, Lausanne, Switzerland, 2019, pp. 189-192 https://t.co/nBleBsXkFf

— Wladek Grabinski (@wladek60) August 26, 2019

The EPFL HEMT Model is a design-oriented charge-based model for dc operation of AlGaAs/GaAs and AlGaN/GaN-based high-mobility field-effect transistors. https://t.co/KoxvcDSPTh https://t.co/c5fUa76rV7 #paper pic.twitter.com/k5U7l3htU6

— Wladek Grabinski (@wladek60) August 23, 2019

#Welsh put £1.3m into #compound process #technology development https://t.co/Jhdwm4WDM8 #paper pic.twitter.com/hmOlw93jdl

— Wladek Grabinski (@wladek60) August 23, 2019

“IEEE EDS MQ at IIT Kanpur:

— Wladek Grabinski (@wladek60) August 23, 2019

B.Iniguez, URV, Spain: Universal TFT compact model

A.Kottantharayil, IIT Bombay: Graphene based devices

A.Dixit, IIT Delhi: Multiple Gate FET Modeling

Y.Chauhan, IIT Kanpur: Negative Capacitance Transistor

https://t.co/bbY1s1g62H #paper

#Compact #Modeling of Drain-Extended MOS Transistor Using BSIM-BULK Model https://t.co/KP3af6KD3E pic.twitter.com/hDA7MDEVnc

— Wladek Grabinski (@wladek60) August 23, 2019

For the #SourceForge August 2019 “Staff Pick” Project of the Month, we selected #Octave Forge, a collection of packages providing extra functionality for #GNU Octave which is a great alternative to MatLab https://t.co/P6SMMrg2nM #paper pic.twitter.com/ujqlq3mfWr

— Wladek Grabinski (@wladek60) August 22, 2019

Engineers make #transistors and electronic devices entirely from #thread https://t.co/Q9QQ7ZZLPs #paper pic.twitter.com/9U75LzDWVT

— Wladek Grabinski (@wladek60) August 21, 2019

Newly discovered properties in the compound uranium ditelluride, or UTe2, show that it could prove highly resistant to one of the nemeses of #quantum #computer development https://t.co/Lul2Op5W6R #paper pic.twitter.com/C1Nz7Cj5TF

— Wladek Grabinski (@wladek60) August 16, 2019

Why Los Angeles #LA decided to #opensource its future https://t.co/1HsXedylg5 pic.twitter.com/KYyrpOgqWo

— Wladek Grabinski (@wladek60) August 15, 2019

Flexible Design Pursues PDK, Power; Battery startups aim to enable #flexible #electronics https://t.co/iVc4Wzr78i #paper pic.twitter.com/Pt78L534lg

— Wladek Grabinski (@wladek60) August 14, 2019

#Huawei to help create nation's first #opensource #foundation https://t.co/OGplZqOI1S pic.twitter.com/Xsdh3Zva8y

— Wladek Grabinski (@wladek60) August 13, 2019

#Huawei announces #opensource Harmony OS https://t.co/3oBWFgcXVc pic.twitter.com/kxN86XBMyO

— Wladek Grabinski (@wladek60) August 12, 2019

Horizon Europe - Commission announces top experts to shape Horizon Europe (2021-2027) missions https://t.co/5s7twEGfG4 #paper pic.twitter.com/YPw6s3cUqX

— Wladek Grabinski (@wladek60) August 1, 2019

8:00 – 8:30 – Registration8:30 – 9:15 – Technology: Guillaume Besnard, SOITEC (F) – UT SOI Processing and Device Fabrication9:15 – 10:00 – Technology: Ahmed Nejim, Silvaco Inc. (USA) – UT SOI TCAD Numerical Process/Device Simulation10:00 – 10:30 – Coffee break10:30 – 11:15 – Devices: Thierry Poiroux, CEA–Leti (F) – Compact modeling for FDSOI technologies: Main challenges and possible solutions11:15 – 12:00 – Devices: Roberto Murphy, INAOE (MX) – RF Electrical Characterization12:30 – 14:00 – Lunch14:00 – 14:45 – Design: Christian Enz, EPFL (CH) – Systematic Design of Low-power Analog/RF CMOS Circuits using the Inversion Coefficient14:45 -15:30 – Design: Humberto Andrade da Fonseca (Cadence, US) – Advanced SOI Design and Reliability/Ageing Simulations15:30 – 16:00 – Coffee break16:00 – 17:00 – Panel discussion

Auditorium Maximum, the conference center of the Jagiellonian Universityul. Krupnicza 33,31-123 Kraków (PL)

https://esscirc-essderc2019.org/how-to-register/

Wladek Grabiński (GMC, CH)Daniel Tomaszewski (ITE, PL)

| Id | Time | Paper Title/Location/Session |

| 5189 | 14:00 - 14:26 | Cryogenic MOSFET Threshold Voltage Model Location: Seminar room Session: Compact Modeling Under Cryogenic Conditions |

| 5246 | 14:26 - 14:53 | Subthreshold Mismatch in Nanometer CMOS at Cryogenic Temperatures Location: Seminar room Session: Compact Modeling Under Cryogenic Conditions |

| 5216 | 14:53 - 15:20 | Test Chip for Identifying Spice-Parameters of Cryogenic BiFET Circuits Location: Seminar room Session: Compact Modeling Under Cryogenic Conditions |

| Id | Time | Paper Title/Location/Session |

| 5226 | 10:20 - 10:53 | First Uni-Traveling Carrier Photodiode Compact Model Enabling Future Terahertz Communication System Design Location: Seminar room Session: Modeling of Compound Semiconductor Devices |

| 5253 | 10:53 - 11:26 | Impact of SiGe HBT Hot-Carrier Degradation on the Broadband Amplifier Output Supply Current Location: Seminar room Session: Modeling of Compound Semiconductor Devices |

| 5180 | 11:26 - 12:00 | Monolithically Integrated GaN Power ICs Designed Using the MIT Virtual Source GaNFET (MVSG) Compact Model for Enhancement-Mode p-GaN Gate Power HEMTs, Logic Transistors and Resistors Location: Seminar room Session: Modeling of Compound Semiconductor Devices |

| Id | Time | Paper Title/Location/Session |

| 5363 | 14:20 - 14:46 | The Synergy SPICE – Compact Models Location: Seminar room Session: Advances in MOSFET Modeling |

| 5141 | 14:46 - 15:13 | Comparison of Modeling Approaches for Transistor Degradation: Model Card Adaptations Vs Subcircuits Location: Seminar room Session: Advances in MOSFET Modeling |

| 5316 | 15:13 - 15:40 | FOSS EKV2.6 Verilog-A Compact MOSFET Model Location: Seminar room Session: Advances in MOSFET Modeling |

| Id | Time | Paper Title/Location/Session |

| 5251 | 10:20 - 10:53 | Compact Analytical Model for Trap-Related Low Frequency Noise in Junctionless Transistors Location: Medium Aula A Session: Modeling of Trap Effects and Noise |

| 5329 | 10:53 - 11:26 | Compact Modeling of Low Frequency Noise and Thermal Noise in Junction Field Effect Transistors Location: Medium Aula A Session: Modeling of Trap Effects and Noise |

| 5239 | 11:26 - 12:00 | Evaluation of Static/Transient Performance of TFET Inverter Regarding Device Parameters Using a Compact Model Location: Medium Aula A Session: Modeling of Trap Effects and Noise |

#IEEE Update of the International Roadmap for Devices and Systems (#IRDS) Sets Course for Computer and Electronics Industry Growth https://t.co/WwvxXl4Sq8 #paper pic.twitter.com/ZOwLjWV0Sr

— Wladek Grabinski (@wladek60) July 23, 2019

Looking for #Quality in #TCAD-Based Papers #IEEE #TED: “What is the definition of high quality?” In this editorial, at least partially, this question is addressed. https://t.co/c1G0YXgIdD #paper pic.twitter.com/MbhLzUa4AZ

— Wladek Grabinski (@wladek60) July 23, 2019

#IBM gives #cancer_killing drug AI project to the #OpenSource community | ZDNet https://t.co/GdgoUmx5UT pic.twitter.com/lfC2v7MuFP

— Wladek Grabinski (@wladek60) July 23, 2019

|

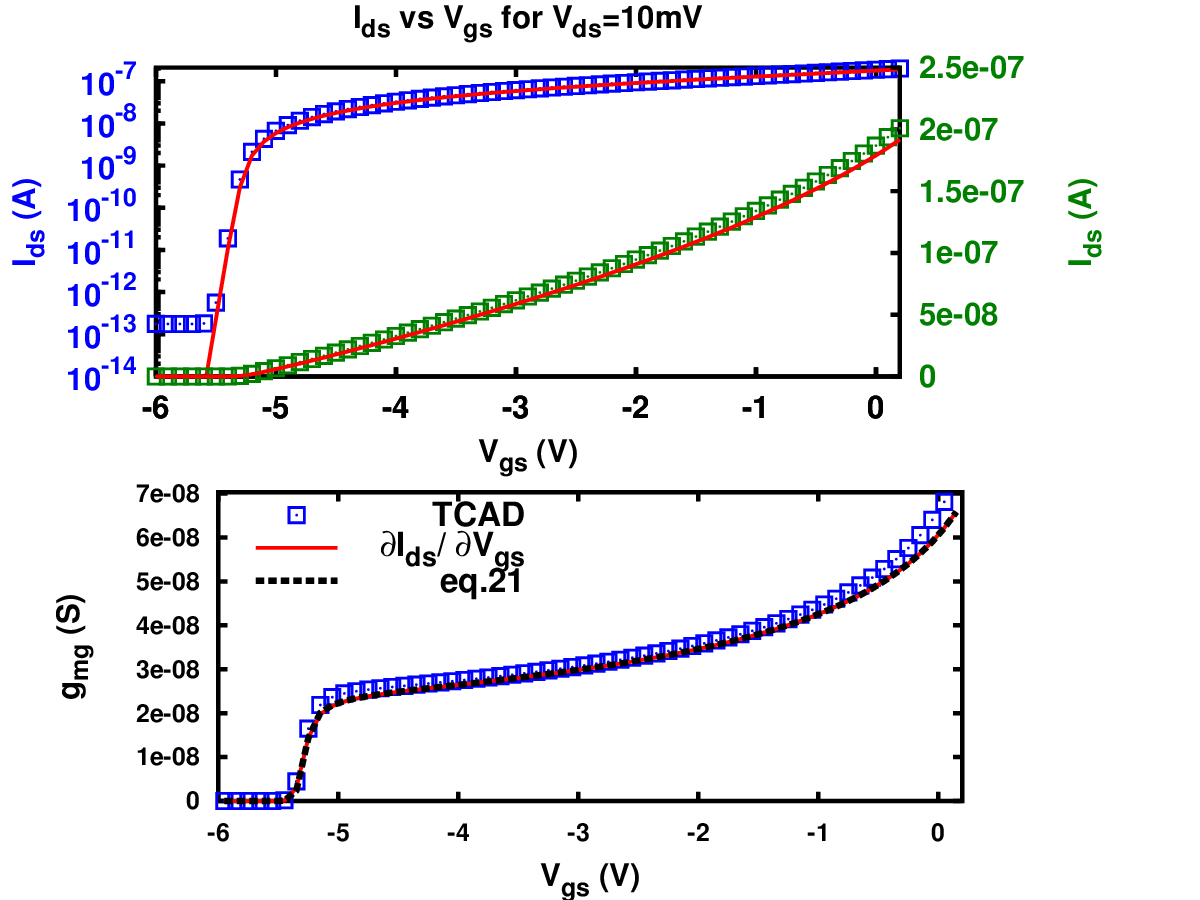

| FIG: IdVg and gmVg at Vd=10mV |

WEBINAR: GPU-Powered SPICE – The Way Forward for Analog Simulation - #Empyrean #Semiwiki https://t.co/JP9u2Tv6Be #paper pic.twitter.com/bY6kqzdFZf

— Wladek Grabinski (@wladek60) July 15, 2019