Circuit Design and Compact Modeling in Printed Electronics Based on Inorganic Materials

PhD Dissertation

Gabriel Cadilha Marques

Veröffentlicht am 30.04.2020

DOI: 10.5445/IR/1000118801

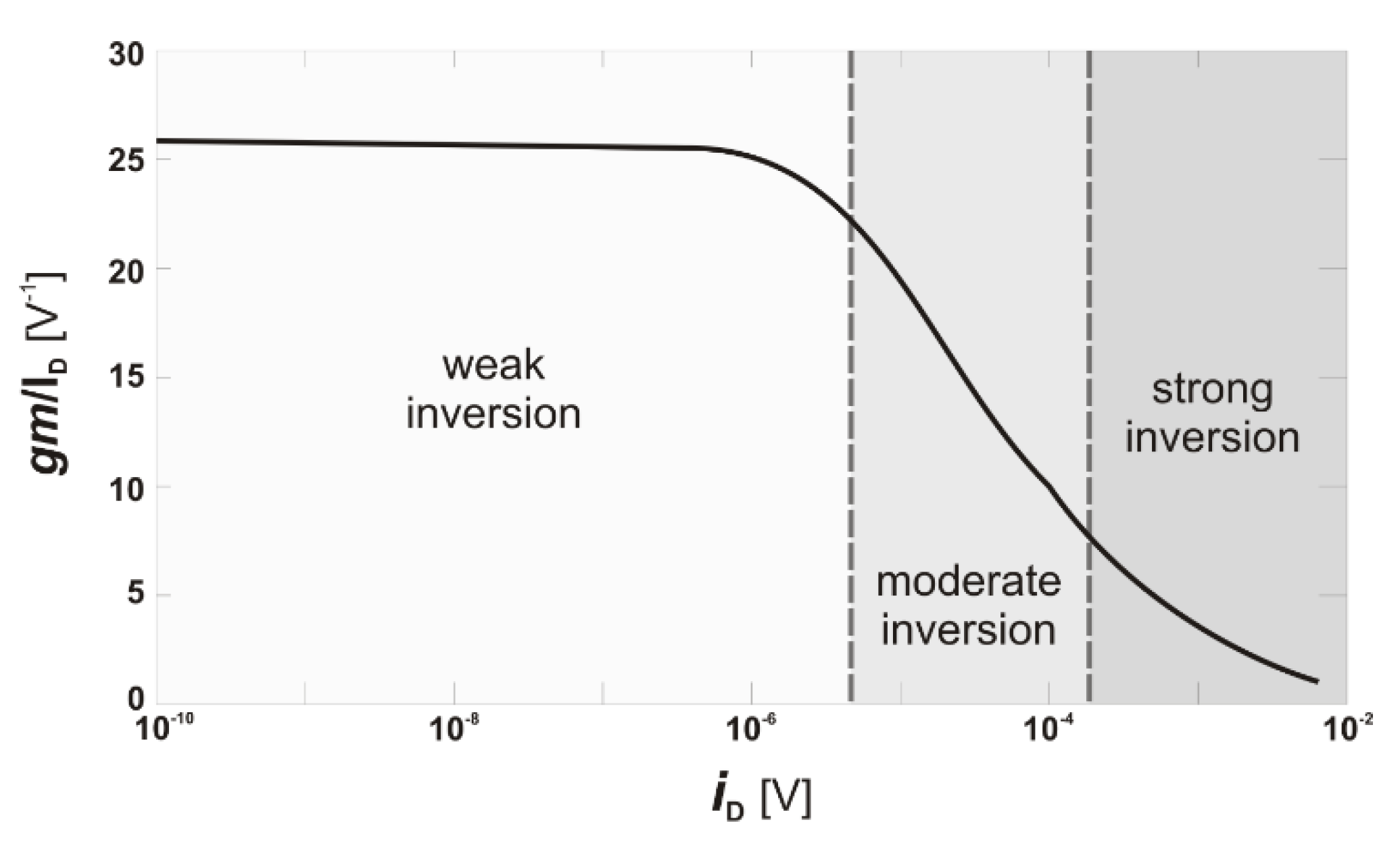

Abstract - The goal of this thesis is therefore to develop an inorganic printed electronics technology with corresponding modeling methodologies to capture device behavior for industry standard circuit simulators as well as circuit designs as building blocks for future applications. To reduce the high supply voltage requirements (~5V) in PE, alternative gating approaches for FETs are considered. One approach is to replace the dielectric with an electrolyte. Due to the formation of a Helmholtz double layer (HDL), a FET with a high gate-capacitance (~5 μFcm-2) is expected, reducing the voltage requirements to ~1V. By combining the indium oxide channel with the electrolyte-gating approach, high performance devices with low voltage requirements are available in PE.