2 Melexis GmbH Erfurt, Erfurt, Germany

Jul 1, 2025

Compact MOSFET Mechanical Stress Model

Bonev, Nikolay, Dirk Michael Nuernbergk, and Christian Lang

Inclusion of Mechanical Stress Effects in a Compact MOSFET Model

Science and Technology 28, no. 2 (2025): 138-149.

DOI: 10.59277/ROMJIST.2025.2.02

2 Melexis GmbH Erfurt, Erfurt, Germany

Abstract: The analog performance of integrated circuits relies on stable parameters of its transistors. Mechanical stress changes the electronic properties of silicon and, therefore, also the device parameters. For circuit design, a good model of these effects is needed for a predictable and reliable function of the circuits. This article extracts the changes of various MOSFET parameters under effect of mechanical stress. A compact description of the stress effects is derived by applying tensors of piezo coefficients. The deviations are included in the physically based compact EKV model. A comparison with measured data shows that the stress effects are modelled correctly within a 10 % error margin.

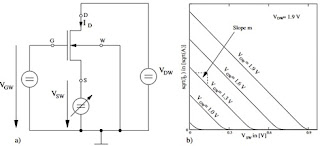

Fig: Extraction setup for the specific current Is

Jun 21, 2025

Technical Lecture - the Celebration of FET100

You are all invited to register and attend the Technical Talks being organized by

IEEE Electron Device Society (EDS) Delhi Chapter – India and IEEE EDS Community Engagement Ad-hoc Committee

along with The National Academy of Sciences, India-Delhi Chapter;

Science Foundation Committee of Deen Dayal Upadhyaya College, University of Delhi, New Delhi, INDIA

Kindly register for each talk separately and forward the email to your students and other colleagues.

Technical Lecture on June 23, 2025 @ 03:00 pm Italy time (GMT +2) i.e. 06:30 pm India Time (GMT +5.30)

The Field Effect Transistor - Evolution of the Modeling Approaches - Massimo Rudan, Professor Emeritus, IEEE Life Fellow, Department DEI, University of Bologna, School of Engineering, Bologna, ItalyRegistration Link to Join the Technical Talk on June 23, 2025 - https://events.teams.microsoft.com/event/ba686434-4454-4641-9781-455ae9a0b322@b51aeb7a-b8a2-4e7d-9a5c-be897389baf0

Technical Lecture on June 25, 2025 @ 12:00 pm Aachen, North Rhine-Westphalia, Germany (GMT +2) i.e. 03:30 pm India Time (GMT +5.30).

A Brief History of Device Simulation for MOSFETs - Christoph Jungemann, RWTH Aachen UniversityRegistration Link to Join the Technical Talk on June 25, 2025 - https://events.teams.microsoft.com/event/2faa8109-5679-4ca2-b883-4255744d3859@b51aeb7a-b8a2-4e7d-9a5c-be897389baf0

Technical Lecture on June 27, 2025 @ 02:00 pm (GMT+2) Time in Stockholm, Sweden i.e. 05:30 pm (GMT + 5:30) Indian Standard Time

Efficient Semiconductor Devices for a Sustainable Future - Professor Mikael Östling, KTH Royal Institute of Technology, FIEEE, School of EECS, Stockholm, SwedenRegistration Link to Join the Technical Talk on June 27, 2025 - https://events.teams.microsoft.com/event/ade77f35-1fb9-4edf-8575-75fcbcbf3dc8@b51aeb7a-b8a2-4e7d-9a5c-be897389baf0

Technical Lecture on June 30, 2025 @ 04:30 pm CET (GMT+2) Time in Madrid, Spain which shall be 08:00 pm Indian Standard Time (GMT +05:30)

History, evolution and perspective of Thin Film Transistor technologies - Benjamin Iñiguez, Universitat Rovira i Virgili, Tarragona, SpainRegistration Link to Join the Technical Talk on June 30, 2025 - https://events.teams.microsoft.com/event/4ae094a9-81c9-408c-8d34-60c307b9e66e@b51aeb7a-b8a2-4e7d-9a5c-be897389baf0

Technical Lecture on July 01, 2025 @ 09:00 am your time (GMT - 5) i.e. 07:30 PM Indian Standard Time (GMT +5:30)

Moore's Law and Radiation Effects on Microelectronics - Daniel M Fleetwood, Olin H. Landreth Professor of Engineering, Professor of Electrical and Computer Engineering, Professor of Physics, Vanderbilt UniversityTechnical Lecture on July 01, 2025 @ 10:00 am (UTC - 5) i.e. 08:30 PM Indian Standard Time (GMT +5:30)

Perovskites – The New Frontier for Solar Photovoltaic Energy Conversion: Science and Technology - Vikram Dalal, Fellow: IEEE, APS, AAAS & Anson Marston Distinguished Professor, Iowa State University, USA

Registration Link to Join the Technical Talk on July 01, 2025 - https://events.teams.microsoft.com/event/65e9fd5e-4922-43be-88e2-1a039ca6bbd7@b51aeb7a-b8a2-4e7d-9a5c-be897389baf0

Technical Lecture on July 2, 2025 @ 4:00 pm Italy time (GMT +2) i.e. 07:30 PM Indian Standard Time (GMT +5:30)

Nanoelectronics and Nanosystems Device Engineering for Sustainability, in the Energy and Variability Efficiency(E.V.E.) Era - Simon Deleonibus, Life Fellow IEEE, Emeritus Fellow Electrochemical Society, Alternatives, Laboratoire d'Electronique et des Technologies de l'Information,(CEA-LETI), Grenoble, France.

Registration Link to Join the Technical Talk on July 02, 2025 - https://events.teams.microsoft.com/event/c2d9a858-4bed-4214-8ec2-d746a99a7a66@b51aeb7a-b8a2-4e7d-9a5c-be897389baf0

Technical Lecture on

July 3, 2025 @ 10:30 am Italy time (GMT - 4) i.e. 08:00 PM Indian Standard Time (GMT +5:30)

Spin-field effect transistor – the unusual FET - Supriyo Bandyopadhyay, Dept. of Electrical and Computer Engineering, Virginia Commonwealth University, Richmond, VA 23284

Spin-field effect transistor – the unusual FET - Supriyo Bandyopadhyay, Dept. of Electrical and Computer Engineering, Virginia Commonwealth University, Richmond, VA 23284

Registration Link to Join the Technical Talk on July 03, 2025 - https://events.teams.microsoft.com/event/dd41911d-528f-4c56-a6a3-7a0a9f43dcc1@b51aeb7a-b8a2-4e7d-9a5c-be897389baf0

-- with regards -- Manoj Saxena

Professor Manoj Saxena | आचार्य मनोज सक्सेना

FNASc(IN), FIETE(IN), SMIEEE(USA)

Department of Electronics | इलेक्ट्रॉनिक्स विभाग

Deen Dayal Upadhyaya College | दीन दयाल उपाध्याय कॉलेज

University of Delhi | दिल्ली विश्वविद्यालय

Dwarka Sector-3, New Delhi-110078 | द्वारका क्षेत्र -३, नई दिल्ली -११००७८

India | भारत

Jun 20, 2025

[C4P] Micro Nano & Chips Tech 2025

|

|

Jun 12, 2025

[mos-ak] [Media Note] MOS-AK INAOE Workshop, Puebla (MX)

MOS-AK INAOE Workshop on Semiconductor Technologies

Puebla (MX), May 14-16, 2025

Media Note

The MOS-AK Workshop on Semiconductor Technologies was held at the Instituto Nacional de Astrofísica, Óptica y Electrónica (INAOE) in Tonantzintla, Puebla, México, on May 14-16, 2025. This workshop was sponsored by MOS-AK, the INAOE, and IEEE through the Puebla Section and the local chapters for the Electron Devices and Instrumentation and Measurements societies. The MOS-AK event was inaugurated by Dr. Wladek Grabinski representing MOS-AK and IHP; Dr. David Sánchez, INAOE's General Director, Dr. Claudia Feregrino, Director of Research and Development for INAOE, and Dr. Roberto Murphy, the local organizer.

The objective of the workshop was to present the various open source tools for the design and simulation of integrated circuits (ICs). It consisted of in person as well as remote keynote speeches by experts in the field, and of a three-hour workshop on digital design synthesis.

The opening talk was by Dr. Wladek Grabinski (MOS-AK), covering a description of all the available FOSS CAD/EDA tools and programs for the design, simulation and fabrication of ICs using OpenPDK. This was a very enlightening run-through of the opportunities that can be exploited by all those who work in the field, at all levels.

It was followed by a conference by Dr. Joaquín Faneca Ruedas, from the Centro Nacional de Microelectrónica (CNM) in Barcelona, Spain. He spoke about silicon nitride photonics, which is fast becoming a scalable platform for integrated optics. We then had the pleasure of listening to Dr. Medhi Saligane talk on agent AI for analog layout generation. Dr. Saligane is now with Brown University in the US. The first day was closed by a talk on memristor modeling by Dr. Arturo Sarmiento from INAOE. Memristors are fast becoming a common element in IC design, and their modeling and eventual characterization has become a very important field of endeavor in recent years.

The second day was opened by Dr. Colin Shaw from Silvaco (US) who gave a deep description of the status of the Si2 Compact Model Coalition.

The rest of the morning was dedicated to a three-hour workshop on digital circuit synthesis using open source CAD/EDA design tools.

Friday's first talk was by Dr. Harriet Parnell, a senior academic engineer at Ansys, and who gave a talk describing Ansys Lumerical FDTD tool, with a case study of a nanohole array. This was followed by a description of logic technology device innovations, given by Dr. Carlos Díaz, the Senior Director for Research and Development for Taiwan Semiconductor Manufacturing Company (TSMC). This great talk was followed by a presentation of the MOSbius project given by Dr. Peter Kinget, the Bernard J. Lechner Professor of Electrical Engineering at Columbia University. The workshop was closed by a researcher at INAOE, Dr. Reydezel Torres, who spoke of the simulation of chip-to-chip interconnects, another very important aspect of semiconductor technology.

The MOS-AK INAOE workshop was attended by 86 participants, mostly undergrad students but also by professional academicians and scientists. We can call it a success, and we hope that it has contributed to the country's much-needed progress in integrated circuit design and technology.

-- R.Murphy and W.Grabinski

-- on the behalf of the MOS-AK INAOE Organizing Committee

RM/WG120625

Jun 11, 2025

[mos-ak] [C4P] 9th Sino MOS-AK Workshop Shenzhen, August 14-16, 2025

Arbeitskreis Modellierung von Systemen und Parameterextraktion

Modeling of Systems and Parameter Extraction Working Group

9th Sino MOS-AK Workshop Shenzhen

August 14-16, 2025

Announcement and C4P

The International MOS-AK Workshop will be held on Aug. 14-16th, 2025 on- the beautiful campus of the Southern University of Science and Technology (SUSTech), Shenzhen, China. With the aggressive scaling of CMOS technologies and constantly emerging diversified devices, accurate device modeling technique poses severe challenge to circuit and system designers, in particular for RF/MW/mmW/THz/Power/optics. The workshop aims to strengthen a network and discussion forum for experts in the field, provide a forum for the presentation and discussion of the leading-edge research and development results of analytical modeling, compact modeling, characterization and simulation techniques for advanced devices, circuits and technologies. In addition to regular papers, MOS-AK Shenzhen 2025 will host three tutorial/workshop sessions on advanced GaN device modeling and circuit design, cryogenic CMOS modeling and circuit design, and millimeter-wave radar applications.

Paper Submission: Authors from both academia and industry are invited to submit technical papers describing original work and/or advanced practices and R&D projects

(any related enquiries can be sent to music@sustech.edu.cn)

Online Registration is open (any related enquiries can be sent to music@sustech.edu.cn)

Important Dates:

- Manuscript submission deadline: 30th June 2025

- Notification of Acceptance: 10th July 2025

- Submission of final manuscript: 15th July 2025

- MOS-AK Workshop: Aug. 14-16th, 2025

-- Xiaoguang Liu, SUSTech and W.Grabinski for Extended MOS-AK Committee

WG110625

Subscribe to:

Comments (Atom)