CODEOCEAN capsule written in OCTAVE which calculates the current and transconductances (gm, gmd and gms) using the charge based approach introduced in [

1]. The capsule generates graphs demonstrating model versus TCAD simulations. The user can use the capsule code to experiment and reproduce the results in the paper [1].

The capsule is provided at the IEEE explorer site under the "Code&Datasets" link. https://ieeexplore.ieee.org/document/8371530 / doi: 10.1109/TED.2018.2838101

Or at the link below https://codeocean.com/capsule/8244803/tree"

|

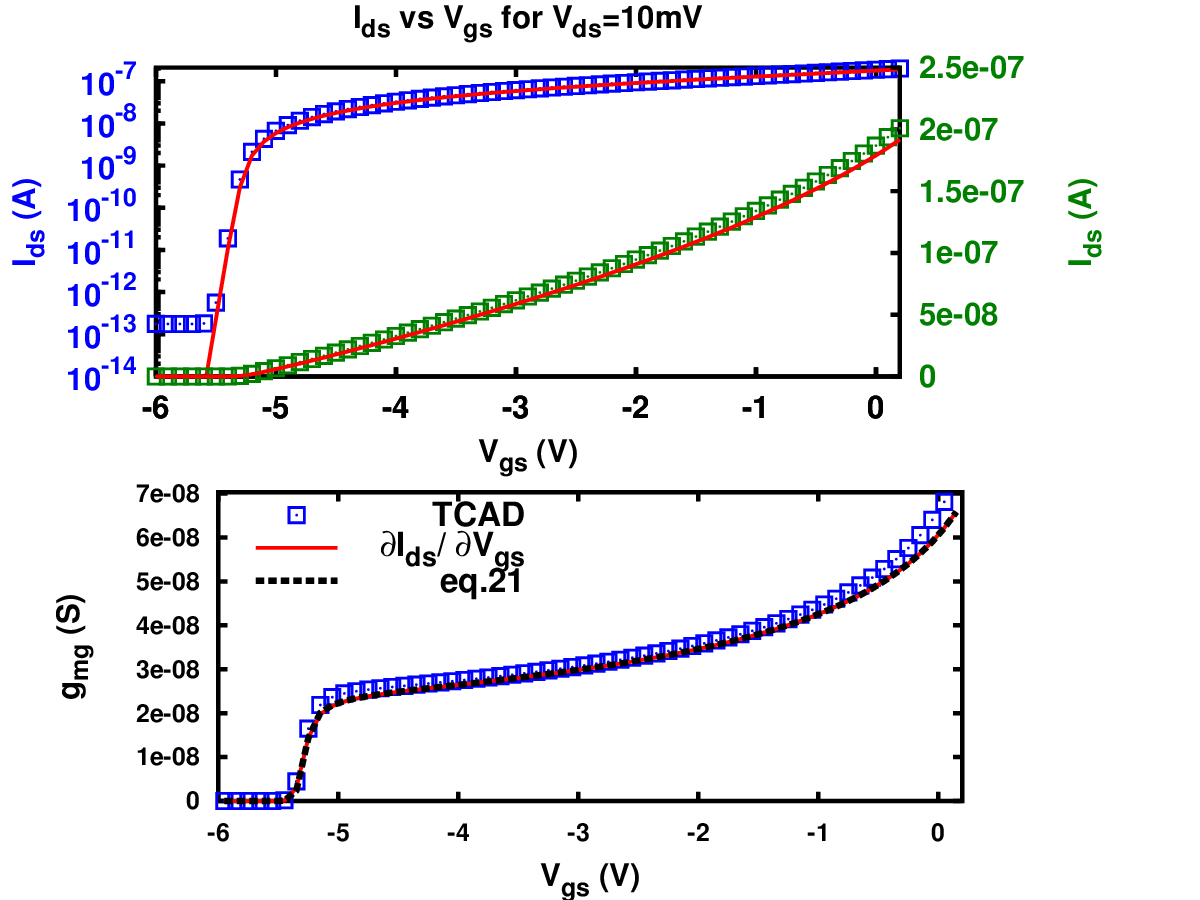

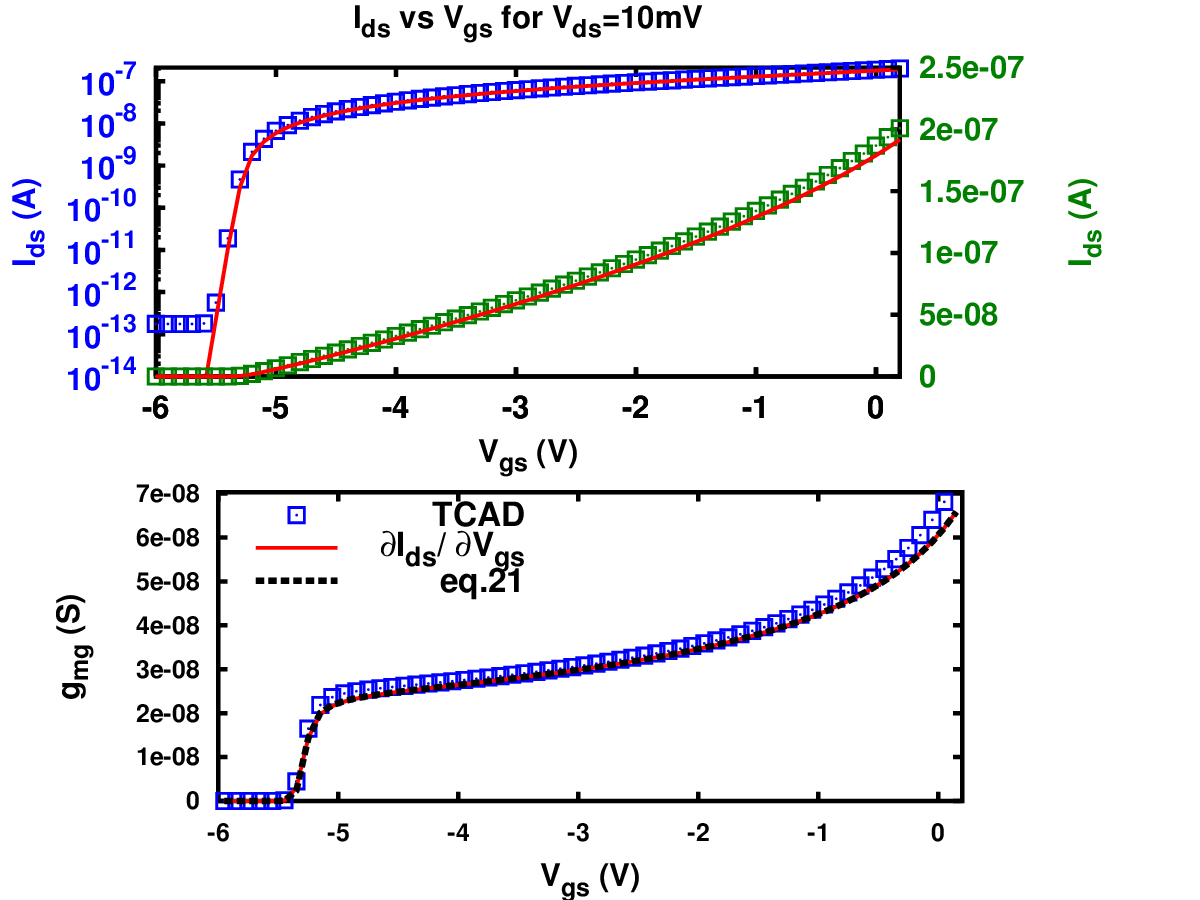

| FIG: IdVg and gmVg at Vd=10mV |

REF:

doi: 10.1109/TED.2018.2838101

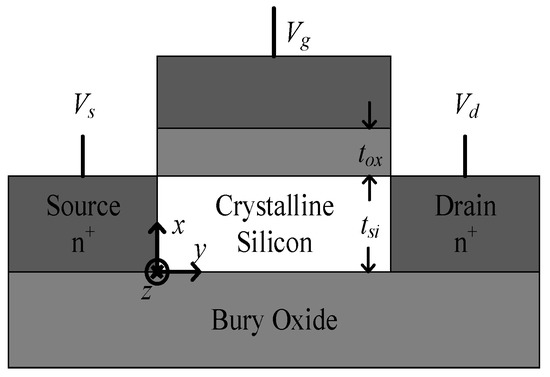

Abstract: The double-gate (DG) junction field-effect transistor (JFET) is a classical electron device, with a simple structure that presents many advantages in terms of not only device fabrication but also its operation. The device has been largely used in low-noise applications, but also more recently, in power electronics. Physics-based compact models for JFETs, contrary to MOSFETs, are, however, scarce. In this paper, an analytical, charge-based model is established for the mobile charges, drain current, and transconductances of symmetric DG JFETs, covering all regions of device operation. The model is unified and continuous from subthreshold to linear and saturation operation and is valid over a large temperature range. This charge-based model constitutes the basis of a full compact model of the DG JFET.

Keywords: junction gate field effect transistors;semiconductor device models;mobile charges;double-gate junction field-effect transistor;classical electron device;low-noise applications;power electronics;long-channel symmetric double-gate junction FET;symmetric DG JFET;charge-based modeling;physics-based compact models;drain current;Electric potential;JFETs;Logic gates;Integrated circuit modeling;Junctions;Mathematical model;MOSFET;Analytical model;circuit simulation;compact model;junction field-effect transistor (JFET);temperature effect