Adelcio M. de Souza, Daniel R. Celino, Regiane Ragi, Murilo A. Romero

Fully analytical compact model for the Q–V and C–V characteristics

of cylindrical junctionless nanowire FETs

Microelectronics Journal (2021): 105324

DOI: 10.1016/j.mejo.2021.105324

University of Sao Paulo (EESC/USP), Sao Carlos (BR)

Abstract: This paper develops a new compact model for the Q–V and C–V characteristics of cylindrical junctionless nanowire FETs in which the nanowire radius is large enough, in such a way that quantum confinement effects can be neglected. Our model is fully analytical and valid for all bias regimes, i.e., subthreshold, partial depletion, and accumulation. The obtained Q-V and C–V characteristics, as well as their derivatives, are continuous across the full range of bias voltages. The model is fully physics-based, with no fitting parameters, and it is very intuitive, since it relies on the understanding of the device as a gated resistor. Model validation is performed against previous results in the literature, demonstrating very good agreement.

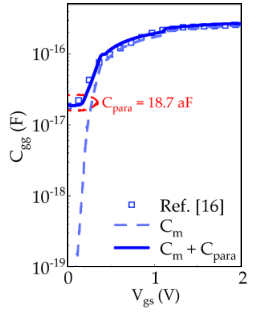

Fig. Validation of our C–V model (solid lines) in comparison to numerical results, highlighting the effect of parasitic capacitance. The free-carrier capacitance component from new model is shown in dashed lines. Simulation parameters: tox = 4.5nm, Nd = 1.6E18 cm−3, L = 200nm, VFB = 1.09V and Vds = 0.05V.

Acknowledgments: The authors would like to thank the Brazilian funding agencies CAPES, CNPq, and Fapesp for their financial support: Conselho Nacional de Desenvolvimento Científico e Tecnologico. Grant Number: 303708/2017-4; Coordenaçao de Aperfeiçoamento de Pessoal de Nível Superior; Fundaçao de Amparo a Pesquisa do Estado de Sao Paulo. Grant Number: 18/13537-6.

No comments:

Post a Comment