Let's welcome them!

They are starting with some interesting papers on low-power and analog design with nanometer-scale variations.... Let's hope they go on...

IEEE Journal of Emerging and Selected Topics in Circuits and Systems (JETCAS)

We are honored to welcome readers and authors to the inaugural issue of the IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS for short), which is sponsored by the IEEE Circuits and Systems Society (CAS-S.)

The journal, which is freely accessible on-line to all CAS-S members, aims to build a platform for the broad and timely dissemination of key innovative results and findings in rapidly-growing and/or emerging topic areas within the scope of the IEEE Circuits and Systems Society. Such potentially interdisciplinary emerging topics will be selected as long as, first, they are clearly situated at the forefront of current scientific and technological developments and, second, they are expected to grow over time in scientific and professional importance and, therefore, in the number of active practitioners. From this point of view, JETCAS is expected to create new communities interested in the long-term development of the most promising subjects presented in the journal. The editorial strategy followed by JETCAS will be the publication of Special Issues on the selected topics. These issues will include research contributions from leading experts and presentations geared towards a wide audience of scientists and pra

MASSOUD PEDRAM, Editor-in-Chief (EiC)

MANUEL DELGADO-RESTITUTO, Deputy EiC

ENRICO MACII, 2010-2011 VP Publications, IEEE CAS-S

GIANLUCA SETTI, 2010 President, IEEE CAS-S

Volume 1, Issue 1 - Inaugural Edition

http://ieeexplore.ieee.org/xpl/RecentIssue.jsp?punumber=5503868

Pedram, M.; Delgado-Restituto, M.; Macii, E.; Setti, G., Inaugural Editorial

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5765455

-----------------------------------------------------------------------------------------------------

Variation-Aware Design for Nanoscale VLSI Circuits and Systems

The focus of this issue is on the challenges faced in designing digital and analog circuits in nanoscale technologies, where variations due to process, environmental, and aging variations are substantial. The root causes of these effects can generally be traced to scaling: with the drive towards even greater miniaturization, these problems become even more acute and it is imperative that they be addressed. The solutions involve the invention of improved design techniques, better design automation, and closer interactions between the phenomenological root causes and the designer. The six papers in this issue attempt to provide a view of the landscape, reflecting the current state of the art and future directions.

Sapatnekar, S. S., Guest Editorial

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5762378

------------------------------------------------------------------------------------------------------------------

Sapatnekar, S. S., Overcoming Variations in Nanometer-Scale Technologies

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5762377

Nanometer-scale circuits are fundamentally different from those built in their predecessor technologies in that they are subject to a wide range of new effects that induce on-chip variations. These include effects associated with printing finer geometry features, increased atomic-scale effects, and increased on-chip power densities, and are manifested as variations in process and environmental parameters and as circuit aging effects. The impact of such variations on key circuit performance metrics is quite significant, resulting in parametric variations in the timing and power, and potentially catastrophic failure due to reliability and aging effects. Such problems have led to a revolution in the way that chips are designed in the presence of such uncertainties, both in terms of performance analysis and optimization. This paper presents an overview of the root causes of these variations and approaches for overcoming their effects.

-----------------------------------------------------------------------------------------------------------------

Karakonstantis, G.; Chatterjee, A.; Roy, K., Containing the Nanometer "Pandora-Box": Cross-Layer Design Techniques for Variation Aware Low Power Systems

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5766061

The demand for richer multimedia services, multifunctional portable devices and high data rates can only been visioned due to the improvement in semiconductor technology. Unfortunately, sub-90 nm process nodes uncover the nanometer Pandora-box exposing the barriers of technology scaling-parameter variations, that threaten the correct operation of circuits, and increased energy consumption, that limits the operational lifetime of today's systems. The contradictory design requirements for low-power and system robustness, is one of the most challenging design problems of today. The design efforts are further complicated due to the heterogeneous types of designs (logic, memory, mixed-signal) that are included in today's complex systems and are characterized by different design requirements. This paper presents an overview of techniques at various levels of design abstraction that lead to low power and variation aware logic, memory and mixed-signal circuits and can potentially assist in meeting the strict power b

-----------------------------------------------------------------------------------------------------------------

Mitra, S.; Brelsford, K.; Kim, Y. M.; Lee, H.-H. K.; Li, Y., Robust System Design to Overcome CMOS Reliability Challenges

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5751208

Today's mainstream electronic systems typically assume that transistors and interconnects operate correctly over their useful lifetime. With enormous complexity and significantly increased vulnerability to failures compared to the past, future system designs cannot rely on such assumptions. For coming generations of silicon technologies, several causes of hardware reliability failures, largely benign in the past, are becoming significant at the system level. Robust system design is essential to ensure that future systems perform correctly despite rising complexity and increasing disturbances. This paper describes three techniques that can enable a sea change in robust system design through cost-effective tolerance and prediction of failures in hardware during system operation: 1) efficient soft error resilience; 2) circuit failure prediction; and 3) effective on-line self-test and diagnostics. The need for global optimization across multiple abstraction layers is also demonstrated.

-----------------------------------------------------------------------------------------------------------------

Seok, M.; Chen, G.; Hanson, S.; Wieckowski, M.; Blaauw, D.; Sylvester, D., CAS-FEST 2010: Mitigating Variability in Near-Threshold Computing

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5762379

Near threshold computing has recently gained significant interest due to its potential to address the prohibitive increase of power consumption in a wide spectrum of modern VLSI circuits. This tutorial paper starts by reviewing the benefits and challenges of near threshold computing. We focus on the challenge of variability and discuss circuit and architecture solutions tailored to three different circuit fabrics: logic, memory, and clock distribution. Soft-edge clocking, body-biasing, mismatch-tolerant memories, asynchronous operation and low-skew clock networks are presented to mitigate variability in the near threshold ${V} _{rm DD}$ regime.

-----------------------------------------------------------------------------------------------------------------

Maricau, E.; Gielen, G., Computer-Aided Analog Circuit Design for Reliability in Nanometer CMOS

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5762376

Integrated analog circuit design in nanometer CMOS technologies brings forth new and significant reliability challenges. Ever-increasing process variability effects and transistor wear-out phenomena such as BTI, hot carrier degradation and dielectric breakdown force designers to use large design margins and to increase the uncertainty on the circuit lifetime. To help designers to tackle these problems at design time (i.e., Design For Reliability, or DFR), accurate transistor aging models, efficient circuit reliability analysis methods and novel design techniques are needed. The paper overviews the current state of the art in DFR for analog circuits. The most important unreliability effects in nanometer CMOS technologies are reviewed and transistor aging models, intended for accurate circuit simulation, are described. Also, efficient methods for circuit reliability simulation and analysis are discussed. These methods can help designers to analyze their circuits and to identify weak spots. Finally, cost-effect

-----------------------------------------------------------------------------------------------------------------

Zhang, X.; Mukadam, M. Y.; Mukhopadhyay, I.; Apsel, A. B., Process Compensation Loops for High Speed Ring Oscillators in Sub-Micron CMOS

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=5756255

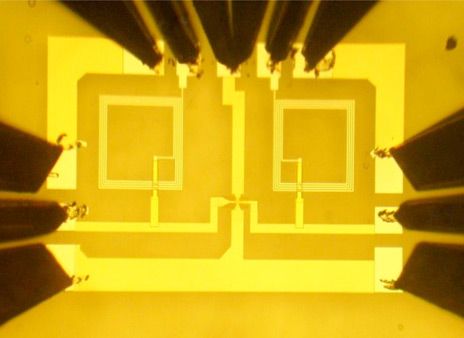

In this paper, we present two implementations of a closed-loop process compensation scheme for high speed ring oscillators-the comparator based and the switched capacitor based loops. We provide detailed discussion of the frequency accuracy, loop stability, and implementation cost for each design. More than 150 test chips from multiple wafer-runs in a 90 nm CMOS process verify that frequency accuracy of better than 2.6% can be achieved with the application of the proposed compensation loop. Moreover, by leveraging a low variation addition-based current source, we have demonstrated a fully-integrated 2.15 GHz ring oscillator with less than 4.6% frequency variation without external references or post fabrication calibration, which is 3.8 $times$ improvement in frequency accuracy over the baseline case. The same compensation scheme can also alleviate frequency drift caused by temperature.

JETCAS is published quarterly and solicits, with particular emphasis on emerging areas, special issues on topics that cover the entire scope of the IEEE Circuits and Systems (CAS) Society, namely the theory, analysis, modeling, design, automation, and implementation of electronic circuits and systems, spanning theoretical foundations, applications, and architectures for signal and information processing.