Highlights

- The cryogenic characterization of SMIC CMOS technology at 4.2K is presented.

- An optimization model VCCS is proposed to calibrate the cryogenic characteristics.

- BP neural network is, for the first time, used in MOSFET modeling.

- The cryo-model can be applied to SPICE simulator and assist in cryo-CMOS circuit design and simulation.

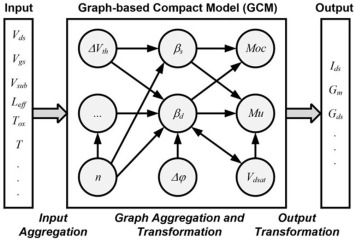

Fig: The structure of graph-based compact model of FinFET. The model receives the input features such as voltages, geometries, etc. as a vector and predicts the drain current (Ids) and its derivatives as output features.

Highlights

- Developed a Graph-based compact model for FinFET.

- Model implemented in Verilog-A for SPICE simulation.

- Requires less number of model parameters and is computationally efficient than BSIM

No comments:

Post a Comment