Oct 4, 2025

[paper] Is there anything left to do in TCAD?

Feb 14, 2025

[paper] Virtual N2 PDK

1 EDA Center, Institute of Microelectronics, Chinese Academy of Sciences, Beijing (CN)

2 School of Integrated Circuits, University of Chinese Academy of Sciences, Beijing (CN)

3 State Key Laboratory of Fabrication Technologies for Integrated Circuits, Beijing (CN)

(b) 111 SRAM cell, (c) 112 SRAM cell, and (d) 122 SRAM cell.

Nov 14, 2024

[paper] TCAD for Circuits and Systems

1 Global TCAD Solutions GmbH., Boesendorferstraße 1/12, 1010 Vienna, Austria

Jan 29, 2024

List of the publications using or referring to DEVSIM

[2] J. Lauwaert; Technology computer aided design based deep level transient spectra: Simulation of high-purity germanium crystals; Journal of Physics D: Applied Physics; (2022) https://doi.org/10.1088/1361-6463/ac34ad

[3] Q. Chen et al.; Analytical model for donor like Gaussian traps in organic thin-film transistor; Organic Electronics; (2021) https://doi.org/10.1016/j.orgel.2022.106464

[4] Q. Chen et al.; The Impact of Contact Position on the Retention Performance in Thin-Film Ferroelectric Transistors; Physica Status Solidi A; (2021) https://doi.org/10.1002/pssa.202100408

[5] L. Hulbert; Designing a Simulator for an Electrically-Pumped Organic Laser Diode; Master’s Thesis; (2019) https://doi.org/10.15368/theses.2019.60

[6] J. E. Sanchez and Q. Chen; Element Edge Based Discretization for TCAD Device Simulation; IEEE Transactions on Electron Devices; (2021) https://doi.org/10.1109/TED.2021.3094776

[7] J. Lauwaert; Fill Factor Loss in a Recombination Junction for Monolithic Tandem Solar Cells; ACS Appl. Energy Mater.; (2023) https://doi.org/10.1021/acsaem.3c00041

[8] J. E. Sanchez; DEVSIM: A TCAD Semiconductor Device Simulator; Journal of Open Source Software; (2022) https://doi.org/10.21105/joss.03898

[9] L. Rickert et al.; High-performance designs for fiber-pigtailed quantum-light sources based on quantum dots in electrically-controlled circular Bragg gratings; Optics Express; (2023) https://doi.org/10.1364/OE.486060

[10] L. R. Brennaman & A. J. Samin; Insights into the performance of InAs-based devices in extreme environments from multiscale simulations; Applied Physics A; (2023) https://doi.org/10.1007/s00339-023-06756-1

[11] M. D. K Jones et al.; Modelling Interfaces in Thin-Film Photovoltaic Devices; Frontiers in Chemistry; (2022) https://doi.org/10.3389/fchem.2022.920676

[12] R. Sellers et al.; fabrication and modeling study to reduce valence band offset in HgCdTe MWIR nBn photodetectors grown on silicon using superlattice barriers; Proc. SPIE PC12687, Infrared Sensors, Devices, and Applications XIII,; (2023) https://doi.org/10.1117/12.2677394

[13] TANG Zhenglai and CAO Bingyang ; Simulations of self-heating effects and the heat generation mechanisms in SOI-MOS devices; Microelectronics & Computer; (2023) https://doi.org/10.19304/J.ISSN1000-7180.2023.0630

[14] Kotecha et al.; Modeling Needs for Power Semiconductor Devices and Power Electronics Systems; IEDM (2019) (2019) https://doi.org/10.1109/IEDM19573.2019.8993449

Jan 15, 2024

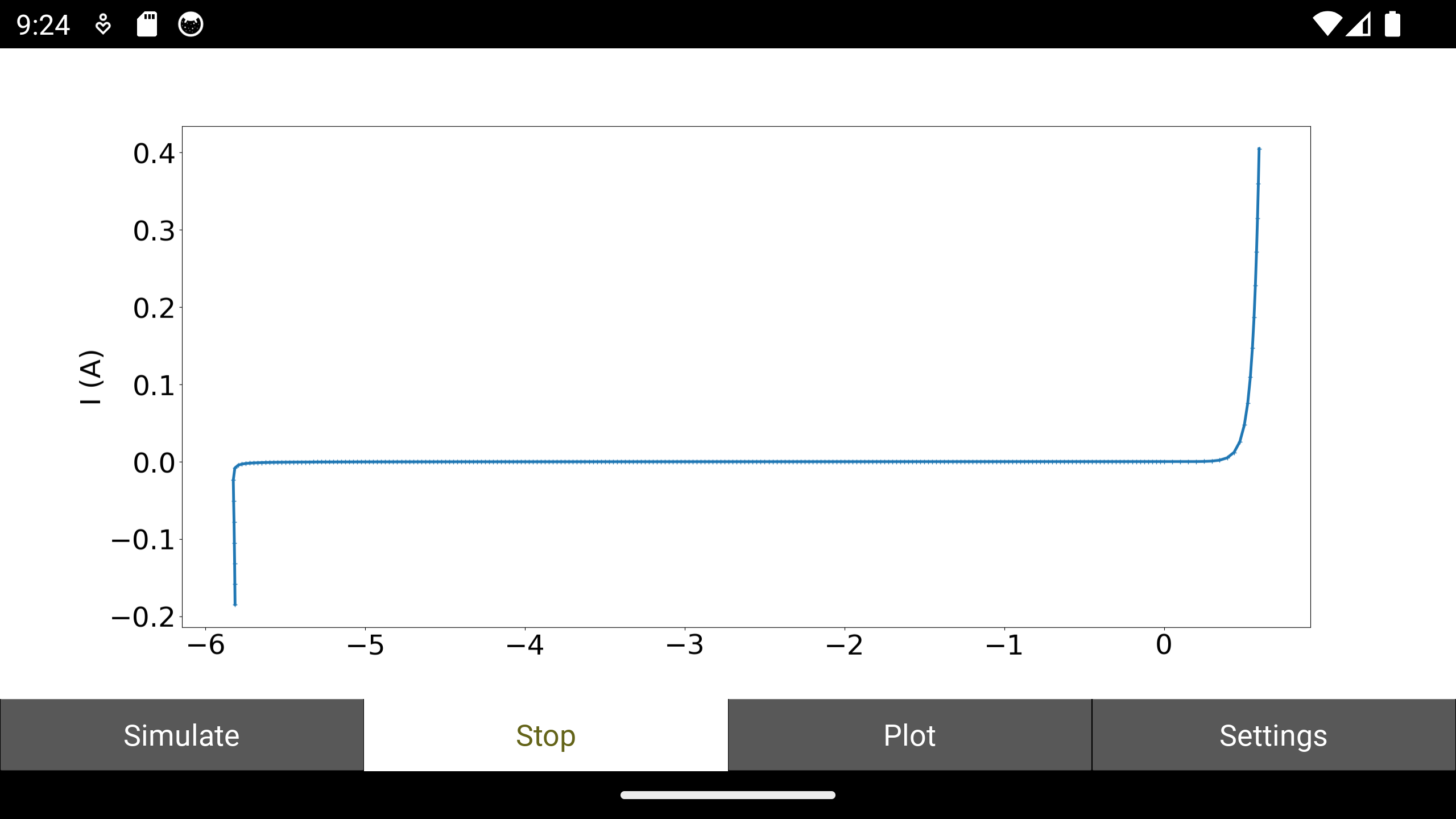

DEVSIM as TCAD mobile app

Now through January 18, 2024, the TCAD app is free for download. After this, you will be entitled to any free future updates [read more...]

- App is renamed to “TCAD app”

- Impact ionization model added

- Menus updated

- Easier plot navigation

- Series resistance available to aid in impact ionization model results

- Stop simulation and keep partial results to stop long-running simulation early

Oct 30, 2023

[paper] DEVSIM

Jun 14, 2023

[review] TCAD Simulations of Semiconductor Piezoresistance

Jun 7, 2023

[paper] Teaching Traditional TCAD New Tricks

1Data and Information Technology Center, Samsung Electronics.

2Device Lab, Samsung Semiconductor Inc.

Mar 3, 2022

[paper] Charge Trapping/Detrapping in Scaled MOSFETs

Oct 20, 2021

[paper] Compact model of 3D NAND

ISRC and School of Electrical Engineering and Computer Science, Seoul National University, (KR)

Jul 26, 2021

[paper] NCFET CMOS Logic

Fig: Equivalent capacitance network and illustrative C-V curve showing NMOS and NC curves. CNC > CINV results in non-hysteretic switching, but low voltage gain in the off-state due to CNC >> COV. Setting CNC to CNC2, which is matched more closely to COV, results in very low SS, but also hysteretic switching as CNC2 < CINV.

Acknowledgment: The authors would like to thank Paul Solomon and Prof. Sayeef Salahuddin for insightful discussions, as well as Synopsys for technical support.

Jun 29, 2021

[paper] Nano Device Simulator

May 25, 2021

[papers] Aging and Device Reliability Compact Modeling

[1] N. Chatterjee, J. Ortega, I. Meric, P. Xiao and I. Tsameret, "Machine Learning On Transistor Aging Data: Test Time Reduction and Modeling for Novel Devices," 2021 IEEE International Reliability Physics Symposium (IRPS), 2021, pp. 1-9, doi: 10.1109/IRPS46558.2021.9405188.

Abstract: Accurately modeling the I-V characteristics and current degradation for transistors is central to predicting circuit end-of-life behavior. In this work, we propose a machine learning model to accurately model current degradation at various stress conditions and extend that to make nominal use-bias predictions. The model can be extended to track and predict any parametric change. We show an excellent agreement of the model with experimental results. Furthermore, we use a deep neural network to model the I-V characteristics of aged transistors over a wide drain and gate playback bias range and show an excellent agreement with experimental results. We show that the model is reliably able to interpolate and extrapolate demonstrating that it learns the underlying functional form of the data.

URL: https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=9405188&isnumber=9405088

[2] P. B. Vyas et al., "Reliability-Conscious MOSFET Compact Modeling with Focus on the Defect-Screening Effect of Hot-Carrier Injection," 2021 IEEE International Reliability Physics Symposium (IRPS), 2021, pp. 1-4, doi: 10.1109/IRPS46558.2021.9405197.

Abstract: Accurate prediction of device aging plays a vital role in the circuit design of advanced-node CMOS technologies. In particular, hot-carrier induced aging is so complicated that its modeling is often significantly simplified, with focus limited to digital circuits. We present here a novel reliability-aware compact modeling method that can accurately capture the full post-stress I-V characteristics of the MOSFET, taking into account the impact of drain depletion region on induced defects.

URL: https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=9405197&isnumber=9405088

[3] Z. Wu et al., "Physics-based device aging modelling framework for accurate circuit reliability assessment," 2021 IEEE International Reliability Physics Symposium (IRPS), 2021, pp. 1-6, doi: 10.1109/IRPS46558.2021.9405106.

Abstract: An analytical device aging modelling framework, ranging from microscopic degradation physics up to the aged I-V characteristics, is demonstrated. We first expand our reliability oriented I-V compact model, now including temperature and body-bias effects; second, we propose an analytical solution for channel carrier profiling which-compared to our previous work-circumvents the need of TCAD aid; third, through Poisson's equation, we convert the extracted carrier density profile into channel lateral and oxide electric fields; fourth, we represent the device as an equivalent ballistic MOSFETs chain to enable channel “slicing” and propagate local degradation into the aged I-V characteristics, without requiring computationally-intensive self-consistent calculations. The local degradation in each channel “slice” is calculated with physics-based reliability models (2-state NMP, SVE/MVE). The demonstrated aging modelling framework is verified against TCAD and validated across a broad range of VG/VD/T stress conditions in a scaled finFET technology.

URL: https://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=9405106&isnumber=9405088

Mar 7, 2021

[C4P] SISPAD 2021, September 27-29

The SISPAD conference series provides an open forum for the presentation of the latest results and trends in process and device simulation. The conference is the leading forum for Technology Computer-Aided Design (TCAD) and is held alternatingly in the United States, Japan, and Europe in September.

Original contributions are solicited for SISPAD 2021 on topics that include but are not limited to:

- Modeling and simulation of established semiconductor device, including FinFETs, GAA FETs, ultra-thin SOI devices, optoelectronic devices, TFTs, sensors, power electronic devices, and organic electronic devices.

- Modeling and simulation of emerging devices including tunnel FETs, SETs, spintronic devices, straintronic devices, bio-electronic devices, and new material-based devices for various applications

- Modeling and simulation of interconnects, including noise and parasitic effects

- Modeling and simulation of all sorts of semiconductor processes, including first principles material design, and growth simulation of nano-scale fabrication

- Advances in fundamental aspects of device modeling and simulation, including of charge, spin, and thermal transport, of collective states including spin/magnetic and charge, and of fluctuation, noise, and reliability.

- Numerical methods and algorithms, including grid generation, user-interface, and visualization

- Compact modeling for circuit simulation, including low-power, high frequency, and power electronics applications

- Process/device/circuit co-simulation in context with system design and verification, including for emerging devices

- Modeling and simulation of equipment, topography, lithography

- Benchmarking, calibration, and verification of simulators

Mar 1, 2021

[papers] compact/SPICE modeling

[1] M. Müller, P. Dollfus and M. Schröter, "1-D Drift-Diffusion Simulation of Two-Valley Semiconductors and Devices," in IEEE Transactions on Electron Devices, vol. 68, no. 3, pp. 1221-1227, March 2021, doi: 10.1109/TED.2021.3051552.

Abstract: A two-valley formulation of 1-D drift-diffusion transport is presented that takes the coupling between the valleys into account via a new approximation for the nonlocal electric field. The proposed formulation is suitable for the simulation of III–V heterojunction bipolar transistors as opposed to formulations that employ the single electron gas approximation with a modified velocity-field model, which also causes convergence problems. Based on Boltzmann transport equation simulations, model parameters of the proposed two-valley formulation are given for GaAs, InP, InAs, and GaSb at room temperature. Applications of the new formulation are also demonstrated.

Code/Dataset: This article contains datasets made available via IEEE DataPort, a repository of datasets intended to facilitate analysis and enable reproducible research. Click the dataset name below to access it on the IEEE DataPort website.

[2] A. Rawat et al., "Experimental Validation of Process-Induced Variability Aware SPICE Simulation Platform for Sub-20 nm FinFET Technologies," in IEEE Transactions on Electron Devices, vol. 68, no. 3, pp. 976-980, March 2021, doi: 10.1109/TED.2021.3053185.

Feb 26, 2021

[DAY 2] 1st Asia/South Pacific MOS-AK Workshop

Day2: FEB.26

Session C Chair: Sadayuki Yoshitomi, Kioxia (J)

[8] eSim: An open source CAD software for circuit simulation

Kannan Moudgalya

IIT Bombay (IN)

[9] A modular approach to next generation Qucs

Felix Salfelder and Mike Brinson

QUCS Team; Centre for Communications Technology, London Metropolitan University (UK)

Tian-Li Wu

National Yang Ming Chiao Tung University, Taiwan (TW)

[11] TCAD-inspired compact modeling approach

Sung-Min Hong and Kwang-Woon Lee

Gwangju GIST (KR)

Session D Chair: Sheikh Aamir Ahsan, NIT Srinagar (IN)

[10] An Innovative Technique for Ultrafast Carrier Dynamics and THz Conductivities of Semiconductor Nanomaterials

Praveen Kr. Saxena and Fanish Kr. Gupta

Tech Next Lab, Lucknow (IN)

Shubham Sahay

IIT Kanpur (IN)

Takayuki Mori and Jiro Ida

Kanazawa Institute of Technology, Nonoichi (J)

[DAY 1] 1st Asia/South Pacific MOS-AK Workshop

DAY 1: FEB. 25, 2021

Session A Chair: Usha Gogineni, ams AG, Hyderabad (IN)

[1] New Insights in Low Frequency Noise Characteristics in PE-BJTs

Peijian Zhang and Ma Long

Science and Technology on Analog Integrated Circuit Laboratory; WHU (CN), Keysight Technologies (US)

[2] Direct white noise characterization of short-channel MOSFETs

K. Ohmori and S. Amakawa

DeviceLab, Tsukuba (J)

[3] SPICE Modeling of 2D-material based FETs with Schottky-barrier contacts

Sheikh Aamir Ahsan

Nanoelectronics Research and Development Group, NIT Srinagar, Jammu and Kashmir (IN)

[4] Physics-based model of SiC MOSFETs including high voltage and current regions

Sourabh Khandelwal, Cristino Salcines, and Ingmar Kallfass

Macquarie University Sydney (AU), University of Stuttgart (D)

Session B Chair: Daniel Tomaszewski, IMiF, Warszaw (PL)

[5] Compact Modeling for Gate-All-Around FET Technology

Avirup Dasgupta

IIT Roorkee (IN)

[6] BSIM-HV: Advanced High Voltage MOSFET Compact Model

Harshit Agarwal

IIT Jodhpur (IN)

[7] ASCENT+ Transnational Access for the nanoelectronics

Georgios Fagas

Tyndall (IE)

Jan 8, 2021

[C4P] New simulation methodologies for next-generation TCAD

• Artificial Intelligence applied to TCAD

• TCAD device models for• Process simulation

• new materials (2D materials, oxides, organic semiconductors, oxide semiconductors,

nanowire devices etc.)

• new device types (magnetic devices, memristors, spintronics, qubits, sensors etc.)

• physical effects (ferroelectric dielectrics, thermal transport at nanoscale, atomistic

simulation etc.)

• simulation conditions that push the limits of standard TCAD: ballistic transport, THz

frequencies, cryogenic conditions, device degradation, electromagnetic and plasma

waves in active devices, transient simulations, noise and fluctuations, microscopic

simulation of large power devices

• Atomistic process simulation to generate structures for atomistic device simulations• New methods for the TCAD tool chain

(including both interconnects and transistors)

• Gate stack modeling including dipole diffusion

• Stress simulation for nanosheet and forksheet devices and stress simulations

including layout effects

• Topological simulation

• Equipment simulation

• Self-consistent integration of simulation models into the hierarchy

• Device-circuit interaction

• Multi-physics and multi-scale integration

• Efficient use of the data produced along the chain

• Workflow improvements

• Methods that improve the turn-around-time for TCAD simulations

using an IEEE style file. Please visit the following link to download the templates:

http://www.ieee.org/publications_standards/publications/authors/author_templates.html

In your cover letter, please indicate that your submission is for this special issue.

1. Prof. Fabrizio Bonani, Politecnico di Torino, Italy

2. Dr. Stephen Cea, Intel Corp., USA

3. Prof. Elena Gnani, University of Bologna, Italy

4. Prof. Sung-Min Hong, GIST, Republic of Korea

5. Dr. Seonghoon Jin, Samsung, USA

6. Prof. Christoph Jungemann, RWTH Aachen, Germany

7. Prof. Xiaoyan Liu, Peking University, China

8. Dr. Victor Moroz, Synopsys, USA

9. Dr. Anne Verhulst, imec, Belgium

Jan 5, 2021

[paper] NESS Open-Source TCAD Environment

Nov 19, 2020

[paper] HEMT RF/Analog Performance

1 Department of Genie Electric and Electronics, Unit Research of Material and Renewable Energies, University Aboubek Belkaid, Tlemcen, Algeria

2 LAAAS Laboratory, University of Batna 2, Batna, Algeria

3 Center Exploitation Telecommunication Satellite– Bouchaoui-Alger, Algeria Space Agency, Algiers, Algeria

4 Center Exploitation Telecommunication Satellite– Oran-Alger, Algeria Space Agency, Algiers, Algeria