Jan 30, 2023

[paper] Zener diode compact modeling and simulation

[paper] DMT-core: A Python Toolkit for Semiconductor Device Engineers

- The analysis/visualization/generation of data becomes difficult to reproduce.

- Device engineers work far from their maximum work-efficiency, as they are hindered, instead of empowered, by the software infrastructure.

- Knowledge built-up, possibly over decades, may be lost when developers leave a company or institution.

- classes and methods relevant to commonly used device engineering tasks

- several abstract base classes for implementing new interfaces to various types of simulators

- concrete implementations of the abstract base classes for open-source simulators such as Ngspice (Vogt, 2022), Xyce (Keiter et al., 2014) or Hdev (Müller et al., 2022).

- for circuit simulations (Weimer et al., 2022),

- for TCAD simulations and plotting (Markus Muller et al., 2021),

- for circuit and TCAD simulations (M. Muller et al., 2022),

- for model parameter extraction (Müller & Schröter, 2019) and

- for model parameter extraction and TCAD simulation (Phillips et al., 2022).

Vogt, H. (2022). Ngspice, the open source Spice circuit simulator - Intro. http://ngspice. sourceforge.net/

Keiter, E. R., Mei, T., Russo, T. V., Schiek, R. L., Sholander, P. E., Thornquist, H. K., Verley, J. C., & Baur, D. G. (2014). Xyce Parallel Electronic Simulator Reference Guide , Version 6 . 2 (September). Sandia National Laboratories (SNL). https://doi.org/10.2172/1826862

Müller, M., Mothes, S., Claus, M., & Schröter, M. (2022). Hdev: A 1D and 2D Hydrodynamic/Drift-Diffusion solver for SiGe and III-V HBTs. J. Open Source Software

Stodden, V., McNutt, M., Bailey, D. H., Deelman, E., Gil, Y., Hanson, B., Heroux, M. A., Ioannidis, J. P. A., & Taufer, M. (2016). Enhancing reproducibility for computational methods. Science, 354(6317), 1240–1241. https://doi.org/10.1126/science.aah6168

Grabinski, W. (2019). FOSS TCAD/EDA tools for compact modeling. Arbeitskreis Bipolar.

https://www.iee.et.tu-dresden.de/iee/eb/forsch/AK-Bipo/2019/7-MOS-AK-Association_wgr_BipAK19.pdf

[paper] ULTRARAM Memory on Silicon

Jan 24, 2023

Mixed Signal SoC design Marathon using eSim & SKY130

Marathon Date : 23 Sept. - 8 Oct. 2022

The following submissions are adjudged as Outstanding, Excellent, Very good and Good by the FOSSEE and the VSD teams.

List of Outstanding Circuits:

| # | Participant | Circuit | Institute | GitHub |

|---|---|---|---|---|

| 1 | Milad Vafaieenezhad | Window Comparator Along with MOD-16 Counter for Counting Based Data Line Selection Operation | Shahed University | View Repo |

| 2 | Krunal Badlani | Crack Sensing Circuit | Indian Institute of Technology Hyderabad | View Repo |

| 3 | Karuppusamy V | Flash Type ADC | Bannari Amman Institute of Technology | View Repo |

| 4 | Inderjit Singh Dhanjal | 32-bit SRAM implementation in eSim using Skywater 130nm CMOS technology | K. J. Somaiya College of Engineering | View Repo |

| 5 | Tanay Das | Design of a Class D Audio Amplifier IC Using Sliding Mode Control and Negative Feedback | Sikkim Manipal Institute of Technology | View Repo |

| 6 | Jayanth Nedunuri | Implementation of 4 bit Two Step Flash ADC | Jyothishmathi institute of Technology and Science | View Repo |

| 7 | Aishwarya Balkrishna Patil | Design and Implementation of Automatic Security Monitoring System | Kolhapur Institute of Technology’s College of Engineering, Kolhapur | View Repo |

| 8 | Swagatika Meher | 3-bit CMOS based TIQ comparator Flash ADC | Odisha University of Technology and Research, Bhubaneswar, Odisha | View Repo |

| 9 | Surya V | 3-bit Flash ADC using ROM-based Encoder | National Institute of Technology, Tiruchirapalli | View Repo |

| 10 | Sanket M Mantrashetti | Design of 8x8 SRAM based on 6T SRAM cell | R. V. College of Engineering | View Repo |

| 11 | Avishek Choudhary | 10-bit C2C DAC | Thapar Institute of Engineering and Technology | View Repo |

| 12 | Nalinkumar S | Implementation of Quadruple - Window Comparator Along with Prioritized MOD-16 Counter for Data Line Multiplexing Operation | Madras Institute of Technology Campus, Anna University | View Repo |

| 13 | Rubankumar D | Astable Multivibrator Along with MOD-16 Counter for Counting Based Data Line Selection Operation | Madras Institute of Technology Campus, Anna University | View Repo |

| 14 | Vanshika Tanwar | Implementation of 3 Bit Flash ADC performed in eSim | Dronacharya Group Of Institutions, Greater Noida | View Repo |

| 15 | Ravi Prakash Vishwakarma | 8 Bit Counter/Ramp Type ADC | Madan Mohan Malaviya University Of Technology | View Repo |

| 16 | E Balakrishna | Implementation of 4 Bit Flash ADC mixed signal circuit using 130nm performed in eSim | Dronacharya Group of Institution, Greater Noida | View Repo |

Contact eSim-fossee:

For more information about the marathon, write to us at contact-esim[at]fossee[dot]in

Jan 19, 2023

Call for Papers - IEEE Special Issue of T-ED

Call for Papers - IEEE Special Issue of T-ED on #Semi #Device #Modeling for #Circuit and #System Design Submission Deadline: 30 April 2023 Learn More & Submit: https://t.co/GdNbNufQxH #ElectronDevicesSociety #ElectronDevices #semiconductor #emergingsem…https://t.co/iGSHSjXaxn

— Wladek Grabinski (@wladek60) Jan 19, 2023

from Twitter https://twitter.com/wladek60

January 19, 2023 at 04:32PM

via IFTTT

#NIST and #Google to Create New Supply of #Chips for Researchers and Startups

#NIST and #Google to Create New Supply of #Chips for Researchers and #Semi Tech Startups https://t.co/hP6Ek2bmVK https://t.co/pdrUROnzzF

— Wladek Grabinski (@wladek60) Jan 19, 2023

from Twitter https://twitter.com/wladek60

January 19, 2023 at 01:35PM

via IFTTT

IEEE EDS MQ at NIT Silchar Silchar, Assam (IN)

| DATES | LOCATION | HOST | REGISTER |

|---|---|---|---|

| Date: 29 Jan 2023

Time:10:00AM to 06:00PM (UTC+05:30) Add Event to Calendar | National Institute of Technology Silchar

Dept of ECE, NIT Silchar Silchar, Assam India 788010 Building: ECE/CSE Building | National Inst of Technology - Silchar, ED15 Kolkata Section Chapter NANO42 Co-sponsored by Dr. Trupti R. Lenka | Starts Dec.1, 2022 Ends Jan.28,2023 No Admission Charge Register NOW |

- Anil Kottantharayil (anilkg@ieee.org)

- Gananath Dash (gndash@ieee.org)

- Ajit Kumar Panda (akpanda62@hotmail.com)

- Manoj Saxena (msaxena@ieee.org)

- Brajesh Kumar Kaushik (bkkaushik23@gmail.com)

- Samar Saha (samar@ieee.org)

- Hiroshi Iwai (h.iwai@ieee.org)

- Taiichi Otsuji (taiichi.otsuji.e8@tohoku.ac.jp)

- Pei-Wen Li (pwli@nycu.edu.tw)

- Zhou Xing (EXZHOU@ntu.edu.sg)

- Albert Chin (albert_achin@hotmail.com)

- Mansun Chan (mchan@ust.hk)

- Chao-Sung LAI (cslai@mail.cgu.edu.tw)

- Wladek Grabinski, MOS-AK, EU (wladek@grabinski.ch)

Jan 18, 2023

Neural networks and machine learning approach for compact modeling

Highlights

- The cryogenic characterization of SMIC CMOS technology at 4.2K is presented.

- An optimization model VCCS is proposed to calibrate the cryogenic characteristics.

- BP neural network is, for the first time, used in MOSFET modeling.

- The cryo-model can be applied to SPICE simulator and assist in cryo-CMOS circuit design and simulation.

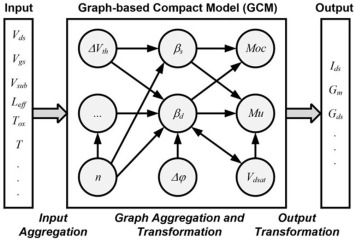

- Developed a Graph-based compact model for FinFET.

- Model implemented in Verilog-A for SPICE simulation.

- Requires less number of model parameters and is computationally efficient than BSIM

[mos-ak] [Prennouncement] 7th Sino MOS-AK Workshop in Nanjing (CN)

Upcoming, subsequent 7th Sino MOS-AK Workshop in Nanjing (CN) aims to strengthen a network and discussion forum among experts in the field, enhance open platform for information exchange related to compact/SPICE modeling and Verilog-A standardization, bring academic and industrial experts in the compact modeling field together, as well as obtain feedback from technology developers, circuit designers, and CAD/EDA tool developers and vendors, in particular using Free open source PDKs.

Topics to be covered include the following among other related to the compact/SPICE modeling and its Verilog-A standardization:

- Compact Modeling (CM) of the electron devices

- Advances in semiconductor technologies and processing

- Verilog-A language for CM standardization

- New CM techniques and extraction software

- Open Source (FOSS) TCAD/EDA modeling and simulation

- CM of passive, active, sensors and actuators

- Emerging Devices, Organic TFT, CMOS and SOI-based memory

- Microwave, RF device modeling, high voltage device modeling

- Nanoscale CMOS, BiCMOS, SiGe, GaN, InP devices and circuits

- Technology R&D, DFY, DFT and reliability/aging IC designs

- Foundry/Fabless Interface Strategies (eg: using Free open source PDKs)

- Call for Papers - Jan 2023

- 2nd Announcement - April 2023

- Final Workshop Program - July 2023

- 7th Sino MOS-AK Workshop - Aug. 11-13, 2023 (online/onsite)

[C4P] IEEE AUTOTESTCON 2023

|

Jan 17, 2023

Untether #AI #SDK Allows Bare-Metal #Programming

Untether #AI #SDK Allows Bare-Metal #Programming https://t.co/bvY91RKIpi #semi https://t.co/9PjNvyah6G

— Wladek Grabinski (@wladek60) Jan 17, 2023

from Twitter https://twitter.com/wladek60

January 17, 2023 at 09:29PM

via IFTTT

UPCOMING – Winter School in III-Sb applications

- Prof. Dr. Manus Hayne, Lancaster University Birth of the ULTRARAM TM Concept

- Prof. Dr. Dieter Bimberg, Technische Universität Berlin Quantum Dot-Based Flash Memories: The Holy Grail at Sunrise?

- Dr. Petr Klenovský, Masaryk University, Brno Modeling Electronic states of IlI-Sb guantum systems on GaP substrate

- Dr. Wladek Grabinski, MOS-AK (EU) FOSS TCAD/EDA Tools for Compact Modeling

- Prof. Vihar Georgiev, James Watt School of Engineering, Glasgow Nano-electronic Simulation Software (NESS): a flexible nano-device simulation platform

- PD Dr. Uwe Bandelow, WIAS Berlin TBA

- Prof. Claudia Dr.axl, Humboldt Universität Berlin Unsupervised learning for insight into high-throughput calculations

- Rabea Pons, Comsol, Göttingen Introduction into COMSOL and hands-on session

- Prof. Dr. Mathieu Luisier, ETH Zürich TBA

- Dr. Marc Bescond, Faculté des Sciences de Saint Jérôme, NQS group, Marseille TBA

- Dr. Chetan Gupta, Micron Technology (R&D) Industry perspective on memory technologies

- Prof. Dr. Jannik Wolters, Deutschen Zentrum für Luft- und Raumfahrt / TU Berlin Quantum Memories and Introduction into Quantum Technologie

Jan 15, 2023

33rd IEEE MIEL 2023

We are pleased to invite you, as an expert in the field of microelectronics, to submit a paper to MIEL 2023 Conference and to encourage colleagues to do it. The deadline for the submission of two page-extended summaries (including figures, tables, and references) is April 28th, 2023.

- December 31, 2022 First Announcement and Call for Papers

- April 28, 2023 Deadline for Receipt of Abstracts

- June 23, 2023 Notification on Acceptance of Papers

- August 31, 2023 Deadline for registration

- August 31, 2023 Deadline for Receipt of Papers

- September 22, 2023 Dispatch of Conference Programme

Best regards,

Vojkan Davidović

Danijel Danković

http://miel.elfak.ni.ac.rs/

Please contact miel@elfak.ni.ac.rs for further information.

Jan 14, 2023

#TSMC is mulling an automotive #semi #fab in #Europe https://t.co/TDeiZXztLu https://t.co/MQ3nH0XlOR

#TSMC is mulling an automotive #semi #fab in #Europe https://t.co/TDeiZXztLu https://t.co/MQ3nH0XlOR

— Wladek Grabinski (@wladek60) Jan 13, 2023

from Twitter https://twitter.com/wladek60

January 14, 2023 at 12:40AM

via IFTTT

Jan 12, 2023

[Paper] Time-Efficient Adaptive Procedure for Identification of Multitone X-Parameters

Abstract: A novel measurement procedure for the time-efficient identification of multitone X-parameters of active microwave devices and circuits is introduced. Over a given bandwidth, the procedure allows for an adaptive selection of key spectral components necessary for determining the X-parameters characteristics with a minimum measurement effort. The sequential selection is based on the divide-and-conquer algorithm. It results in a huge reduction of the measurement time in comparison to the situation when model coefficients at all spectral components are identified. To validate the procedure, an off-the-shelf broadband power amplifier (PA) was characterized under wideband large-signal excitation conditions. Moreover, small-signal terms at all relevant frequencies were collected as a reference and compared with the results provided by a time-efficient adaptive procedure (TEAP). The proposed method resulted in twenty times reduction in the number of samples required to characterize the PA. As an application example, the small-signal coefficients identified with the TEAP are used to correct characterization results for the measurement instrument’s output mismatch. The mismatch-corrected output signal of the PA under test was represented accurately with the error-vector-magnitude of only 0.132%.

Jan 11, 2023

[paper] Discovery of Clustered-P1 Borophene and Its Application as the Lightest High-Performance Transistor

[paper] Sirsha Guha, Arnab Kabiraj, and Santanu Mahapatra; Discovery of Clustered-P1 Borophene and Its Application as the Lightest High-Performance Transistor; ACS Appl. Mater. Interfaces 2023, https://t.co/bXA5IFpJVZ https://t.co/ekkSO8Ru8T #semi https://t.co/pyinJ5fvMQ

— Wladek Grabinski (@wladek60) Jan 11, 2023

from Twitter https://twitter.com/wladek60

January 11, 2023 at 04:05PM

via IFTTT

Jan 10, 2023

At the outer edges of Moore’s Law

At the outer edges of Moore’s Law, connecting components is increasingly the game https://t.co/7Tu0CgD60N #semi #interconnects https://t.co/OSFntG8sJ5

— Wladek Grabinski (@wladek60) Jan 10, 2023

from Twitter https://twitter.com/wladek60

January 10, 2023 at 03:15PM

via IFTTT

A #Bayesian machine based on #memristors https://t.co/i3BwR9lwVH #semi https://t.co/UQS1FXiu4N

A #Bayesian machine based on #memristors https://t.co/i3BwR9lwVH #semi https://t.co/UQS1FXiu4N

— Wladek Grabinski (@wladek60) Jan 9, 2023

from Twitter https://twitter.com/wladek60

January 09, 2023 at 11:10PM

via IFTTT

Jan 9, 2023

[ISSCC] First Annual EPFL and ETHZ Friend and Alumni Aperitif

Event Details

Time: Monday (Feb 20th) 5-8pmThere will be food and an open bar!

Location: San Francisco Marriott Marquis, 2nd floor Foothill D