Joint ESSDERC/ESSCIRC Tutorial:

Nanoscale Technology – Transistor Modeling – IC Design

Auditorium Maximum, the Jagiellonian University

Krakow (PL) on Sept.23, 2019

Together with local organization team, MOS-AK Association invites you to Joint ESSDERC/ESSCIRC Tutorial: Nanoscale Technology – Transistor Modeling – IC Design which will be organized at Auditorium Maximum of the Jagiellonian University in Krakow (PL) on Sept.23, 2019

Our joint ESSDERC/ESSCIRC Tutorial aims to provide in-depth coverage of highly relevant R&D topics by world-class experts. We will discuss and present the frontiers of electron device modeling with emphasis on the complete UT SOI development chain, reviewing the nanoscale level technologies, devices TCAD numerical simulations, thru its simulation-aware compact/SPICE modeling up to selected topics of the transistor level IC design for advanced applications. This joint tutorial is designed for academic researchers, device process engineers who are interested in device modeling; academic/industrial ICs designers (to explore RF/Analog/Mixed-Signal) and those starting in these areas as well as device fabrication, electrical characterization, modeling and parameter extraction engineers. The content will be beneficial for anyone who needs to learn what is really behind the IC fabrication and its simulation in using modern SPICE/Verilog-A device models (tutorial agenda listed below).

Joint ESSDERC/ESSCIRC Tutorial will be followed (Sept. 24-26, 2019) by four TRACK4: "'Compact Modeling of Devices and Circuits" Sessions with invited talk "The Synergy SPICE – Compact Models" by Prof. Andrei Vladimirescu and 11 regular conference papers (see all the details below)

Tutorial Agenda:

Our joint ESSDERC/ESSCIRC Tutorial aims to provide in-depth coverage of highly relevant R&D topics by world-class experts. We will discuss and present the frontiers of electron device modeling with emphasis on the complete UT SOI development chain, reviewing the nanoscale level technologies, devices TCAD numerical simulations, thru its simulation-aware compact/SPICE modeling up to selected topics of the transistor level IC design for advanced applications. This joint tutorial is designed for academic researchers, device process engineers who are interested in device modeling; academic/industrial ICs designers (to explore RF/Analog/Mixed-Signal) and those starting in these areas as well as device fabrication, electrical characterization, modeling and parameter extraction engineers. The content will be beneficial for anyone who needs to learn what is really behind the IC fabrication and its simulation in using modern SPICE/Verilog-A device models (tutorial agenda listed below).

Joint ESSDERC/ESSCIRC Tutorial will be followed (Sept. 24-26, 2019) by four TRACK4: "'Compact Modeling of Devices and Circuits" Sessions with invited talk "The Synergy SPICE – Compact Models" by Prof. Andrei Vladimirescu and 11 regular conference papers (see all the details below)

Tutorial Agenda:

8:00 – 8:30 – Registration8:30 – 9:15 – Technology: Guillaume Besnard, SOITEC (F) – UT SOI Processing and Device Fabrication9:15 – 10:00 – Technology: Ahmed Nejim, Silvaco Inc. (USA) – UT SOI TCAD Numerical Process/Device Simulation10:00 – 10:30 – Coffee break10:30 – 11:15 – Devices: Thierry Poiroux, CEA–Leti (F) – Compact modeling for FDSOI technologies: Main challenges and possible solutions11:15 – 12:00 – Devices: Roberto Murphy, INAOE (MX) – RF Electrical Characterization12:30 – 14:00 – Lunch14:00 – 14:45 – Design: Christian Enz, EPFL (CH) – Systematic Design of Low-power Analog/RF CMOS Circuits using the Inversion Coefficient14:45 -15:30 – Design: Humberto Andrade da Fonseca (Cadence, US) – Advanced SOI Design and Reliability/Ageing Simulations15:30 – 16:00 – Coffee break16:00 – 17:00 – Panel discussion

Venue:

Auditorium Maximum, the conference center of the Jagiellonian Universityul. Krupnicza 33,31-123 Kraków (PL)

Online registrations will be accepted until 20 August 2019.

https://esscirc-essderc2019.org/how-to-register/

On the behalf of the local organization team

Wladek Grabiński (GMC, CH)Daniel Tomaszewski (ITE, PL)

ESSDERC/ESSCIRC

TRACK4: Compact Modeling of Devices and Circuits

TRACK4: Compact Modeling of Devices and Circuits

| Id | Time | Paper Title/Location/Session |

| 5189 | 14:00 - 14:26 | Cryogenic MOSFET Threshold Voltage Model Location: Seminar room Session: Compact Modeling Under Cryogenic Conditions |

| 5246 | 14:26 - 14:53 | Subthreshold Mismatch in Nanometer CMOS at Cryogenic Temperatures Location: Seminar room Session: Compact Modeling Under Cryogenic Conditions |

| 5216 | 14:53 - 15:20 | Test Chip for Identifying Spice-Parameters of Cryogenic BiFET Circuits Location: Seminar room Session: Compact Modeling Under Cryogenic Conditions |

| Id | Time | Paper Title/Location/Session |

| 5226 | 10:20 - 10:53 | First Uni-Traveling Carrier Photodiode Compact Model Enabling Future Terahertz Communication System Design Location: Seminar room Session: Modeling of Compound Semiconductor Devices |

| 5253 | 10:53 - 11:26 | Impact of SiGe HBT Hot-Carrier Degradation on the Broadband Amplifier Output Supply Current Location: Seminar room Session: Modeling of Compound Semiconductor Devices |

| 5180 | 11:26 - 12:00 | Monolithically Integrated GaN Power ICs Designed Using the MIT Virtual Source GaNFET (MVSG) Compact Model for Enhancement-Mode p-GaN Gate Power HEMTs, Logic Transistors and Resistors Location: Seminar room Session: Modeling of Compound Semiconductor Devices |

| Id | Time | Paper Title/Location/Session |

| 5363 | 14:20 - 14:46 | The Synergy SPICE – Compact Models Location: Seminar room Session: Advances in MOSFET Modeling |

| 5141 | 14:46 - 15:13 | Comparison of Modeling Approaches for Transistor Degradation: Model Card Adaptations Vs Subcircuits Location: Seminar room Session: Advances in MOSFET Modeling |

| 5316 | 15:13 - 15:40 | FOSS EKV2.6 Verilog-A Compact MOSFET Model Location: Seminar room Session: Advances in MOSFET Modeling |

| Id | Time | Paper Title/Location/Session |

| 5251 | 10:20 - 10:53 | Compact Analytical Model for Trap-Related Low Frequency Noise in Junctionless Transistors Location: Medium Aula A Session: Modeling of Trap Effects and Noise |

| 5329 | 10:53 - 11:26 | Compact Modeling of Low Frequency Noise and Thermal Noise in Junction Field Effect Transistors Location: Medium Aula A Session: Modeling of Trap Effects and Noise |

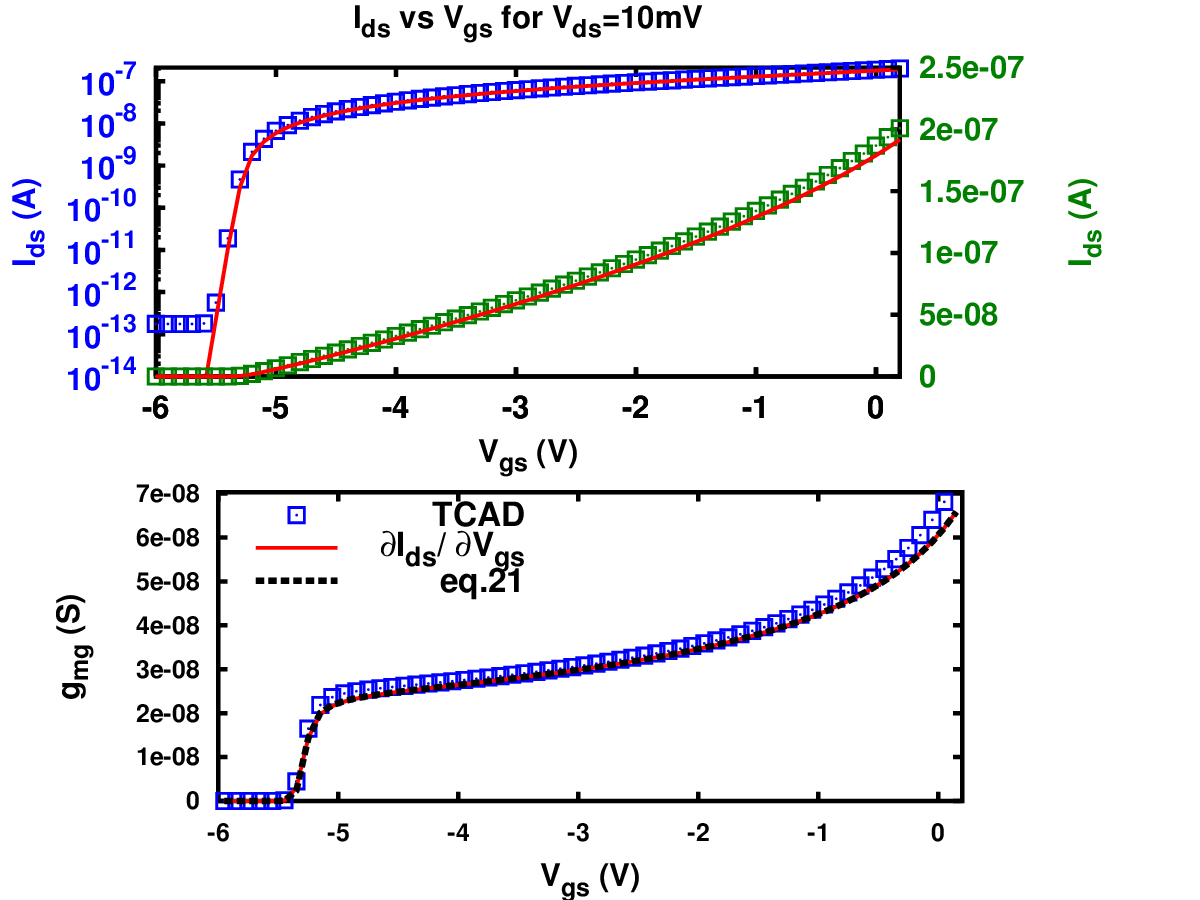

| 5239 | 11:26 - 12:00 | Evaluation of Static/Transient Performance of TFET Inverter Regarding Device Parameters Using a Compact Model Location: Medium Aula A Session: Modeling of Trap Effects and Noise |

You received this message because you are subscribed to the Google Groups "mos-ak" group.

To unsubscribe from this group and stop receiving emails from it, send an email to mos-ak+unsubscribe@googlegroups.com.

To view this discussion on the web visit https://groups.google.com/d/msgid/mos-ak/4a7d94d9-f155-4b65-b64a-43c423071cc4%40googlegroups.com.