Arbeitskreis Modellierung von Systemen und Parameterextraktion

Modeling of Systems and Parameter Extraction Working Group

MOS-AK/ESSERC Workshop in Munich

September 8, 2025

Scheduled consecutive 22nd MOS-AK/ESSERC SPICE/Compact Modeling T2 Workshop organized in Munich, aims to strengthen a network and discussion forum among experts in the field, enhance open platform for information exchange related to compact/SPICE modeling and Verilog-A standardization, bring people in the compact modeling field together, as well as obtain feedback from technology developers, circuit designers, and FOSS CAD/EDA tool developers and vendors. The content will be beneficial for anyone who needs to learn what is really behind the FOSS CAD/EDA IC simulation in modern device models in OpenPDKs. The MOS-AK workshop program is available online:

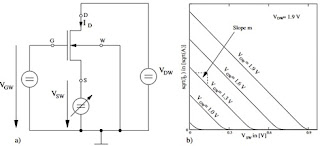

It will be followed by ESSERC T2 Tutorial "Design and Simulation of Analog/RF Integrated Circuits with Open-Source CAD Tools and Process Design Kits". T2 tutorial explores how FOSS CAD/EDA tools and OpenPDKs empower IC designers. T2 also introduces ACM2, a compact, physics-based MOSFET model, with hands-on guidance on design parameter extraction for analog/RF circuit applications using the IHP OpenPDK 130nm BiCMOS process.

Online Registration is open (Early: until Friday July 18, 2025 (23:59 CEST))

any related enquiries can be sent to registration@mos-ak.org

-- W.Grabinski on the behalf of International MOS-AK TPC Committee

WG140725