Apr 26, 2022

[paper] Universal Charge Model for Multigate MOS Structures

[paper] DL Physics-Driven MOSFET Modeling

Mar 1, 2022

[paper] Multi-Segment TFT Compact Model for THz Applications

1 RPI, Troy, NY 12180, USA

2 Norwegian University of Science and Technology, Trondheim, Norway

3 Electronics of the Future, Inc., USA

(b) equivalent circuit for each segment including leakage components

Feb 9, 2022

[paper] SPICE simulation of PIN diodes and IGBT devices

North China Electric Power University, Beijing 102206, China

Abstract: In SPICE simulations of PIN diodes and IGBT devices using finite difference method, one discretizes an undepleted N- region into several equally spaced nodes with a time-dependent distance of Δx(t). Then transforms the ambipolar diffusion equation, a time-space partial differential equation, into a set of time-dependent ordinary differential equations. However, the time-dependent property of Δx(t) destroys the carrier number conservation. In this paper, we propose an approach to account for the effect of the Δx(t) by introducing an auxiliary system. It has the same total current and the total carrier number in the undepleted N- region as the real system, but has different electron and hole current components. The difference is caused by adding compensation current terms with the equal amplitude and opposite sign to the electron and hole current terms in the auxiliary system. These compensation current terms are proportional to the boundary speed of the undepleted N- region and do not change the total current. The auxiliary system can be easily solved using SPICE behavior models and its carrier density is a good approximation to the real one. Our simulations show that the compensation current correction is important for fast switching PIN diodes, but may not be very important in IGBT devices due to their large gate-related capacitance.

Jan 5, 2022

[book] Advanced ASM-HEMT Model for GaN HEMTs

Table of contents:

- Front Matter; pp. i-xv

- Gallium Nitride Semiconductor Devices; pp. 1-8

- Compact Modeling; pp. 9-19

- Introduction to ASM-HEMT Compact Model; pp. 21-31

- Core Formulations in ASM-HEMT Model; pp. 33-45

- Non-ideal Effects in Device Current and Their Modeling; pp. 47-62

- Trapping Models; pp. 63-81

- Non-Ideal Effects in GaN Capacitances and Their Modeling; pp. 83-100

- Gate Current Model; pp. 101-113

- Effect of Ambient Temperature on GaN Device; pp. 115-124

- Noise Models; pp. 125-130

- Parameter Extraction in ASM-HEMT Model; pp. 131-150

- Advance Simulations with ASM-HEMT Model; pp. 153-174

- Resources for ASM-HEMT Model Users; pp. 175-175

- Back Matter; pp. 175-188

Dec 8, 2021

Guardian of Verilog-A Compact Models

Nov 9, 2021

8th EuroSOI-ULIS 2022 at University of Udine (Italy)

| Organized

by:

University of Udine (Italy) Conference chair: Pierpaolo Palestri Local organizing Committee: Francesco Driussi Conference Secretariat: Centro Congressi Internazionali Steering Committee:

|

8th Joint

International EuroSOI Workshop and International Conference on Ultimate Integration on Silicon (EuroSOI-ULIS) 2022 May 18-20, 2022 – Udine, Italy https://eurosoiulis2022.com The Conference aims at gathering

together scientists and engineers working in academia, research centers

and industry in the field of SOI technology and nanoscale devices in

More-Moore and More-Than-Moore scenarios. High quality contributions in the following areas are

solicited:

Original 2-page abstracts with

illustrations will be reviewed by the Scientific Committee. The

accepted contributions will be published as 4-page letters in a special

issue of the Elsevier journal Solid-State Electronics.

Extended versions of outstanding papers will be published in a further

special issue of Solid-State Electronics. A best poster award will be

attributed by ELSEVIER.

The “Androula

Nassiopoulou Best Paper Award" will be attributed by the

SINANO institute.

Important dates:

|

Oct 26, 2021

conference paper reached 400 reads

Oct 7, 2021

[paper] Compact Schottky-barrier CNTFET Modeling

CEDIC, Technische Universität Dresden (D)

Oct 4, 2021

[paper] Flexible Megahertz Organic Transistors

1NanoP, TH Mittelhessen University of Applied Sciences, Gießen 35390, Germany

2Center for Nano Science and Technology @PoliMi, Istituto Italiano di Tecnologia, Milano 20133, Italy

3Max Planck Institute for Solid State Research, Stuttgart 70569, Germany

4DEEA, Uniersitat Rovira i Virgili, Tarragona 43007, Spain

5Georg August University of Goettingen, Goettingen 37077, Germany

Jul 13, 2021

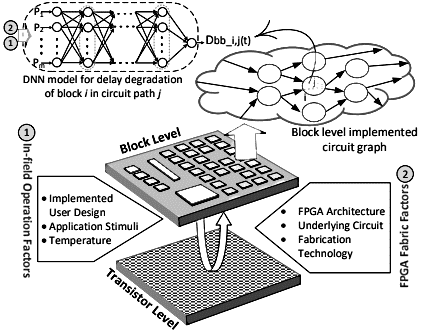

[paper] ML based Aging-Aware FPGA Framework

Jul 1, 2021

[papers] Compact/SPICE Modeling

DOI: 10.1109/USBEREIT51232.2021.9455091.

[2] L. Liu, Y. Tian and W. Huang, "A Bio-IA with Fast Recovery and Constant Bandwidth for Wearable Bio-Sensors," in IEEE Sensors Journal,

DOI: 10.1109/JSEN.2021.3092001.

[3] C. -T. Tung, H. -Y. Lin, S. -W. Chang and C. -H. Wu, "Analytical modeling of tunnel-junction transistor lasers," in IEEE Journal of Selected Topics in Quantum Electronics,

DOI: 10.1109/JSTQE.2021.3090527.

DOI: 10.1016/j.spmi.2021.106975

Jun 11, 2021

[paper] SPICE Modeling of Cycle-to-Cycle Variability in RRAM Devices

a) Departament d’Enginyeria Electrònica, Universitat Autònoma de Barcelona, 08193 Cerdanyola del Valles, Spain

b) Institut de Microelectrònica de Barcelona, IMB-CNM, CSIC, 08193 Cerdanyola del Valles, Spain

Abstract: In this work, we investigated how to include uncorrelated cycle-to-cycle (C2C) variability in the LTSpice quasi-static memdiode model for RRAM devices. Variability in the I-V curves is first addressed through an in-depth study of the experimental data using the FITDISTRPLUS package for the R language. This provides a first approximation to the identification of the most suitable model parameter distributions. Next, the selected candidate distributions are incorporated into the model script and used for carrying out Monte Carlo simulations. Finally, the experimental and simulated observables (set and reset currents, transition voltages, etc.) are statistically compared and the model estimands recalculated if it is necessary. Here, we put special emphasis on describing the main difficulties behind this seemingly simple procedure.

Acknowledgements: This work was supported by the Spanish Ministry of Science, Innovation and Universities through projects TEC2017-84321-C4-1-R, TEC2017-84321-C4-4-R, and PID2019-103869RB-C32.

May 18, 2021

[paper] Generalized Devices for SPICE Simulation of Soft Errors

Abstract: Recent advances in CMOS scaling have made circuits more and more sensitive to errors and dysfunction caused by ionizing radiation, even at ground level, requiring accurate modeling of such effects. Besides generation, transport, and collection of radiation-induced excess carriers, another phenomenon, called funneling, has to be modeled for an accurate prediction of soft errors. The funneling effect occurs when the radiation track crosses a space charge region and generates excess carriers with a density higher than the doping close to it. These carriers distort the electric field of the space charge region, deeply changing the transport mechanism, from diffusion in a field-free semiconductor to drift. The objective of this work is to include funneling as part of the generalized lumped devices model in order to obtain a complete tool for SPICE-compatible simulations of single-event effects (SEEs). The latter approach has been recently proposed to simulate radiation-induced charges in the silicon substrate and is based on the so-called generalized lumped devices that simulate charge generation, propagation, and collection using standard circuit simulators. The generalized devices are here extended to include funneling and used to simulate an alpha particle impinging on the bulk of nMOS and pMOS transistors. The results obtained are validated with TCAD numerical simulations. Finally, a static random-access memory (SRAM) struck by an alpha particle is analyzed. The model predicts that the occurrence of a soft error, i.e., flipping of memory state, may depend on whether or not there is funneling. This justifies the need for accurate modeling of funneling phenomena to predict SEEs in ICs.

FIG: Generalized devices network obtained for the pMOS substrate. The mesh is drawn in gray dashed lines. The network is not shown around the radiation track; only the mesh is reported, which is denser to linearize the generation profile and excess carrier gradients.

Aknowlwdgement: This work was supported by the Swiss National Science Foundation (NSF) under Grant 200021_165773.

May 5, 2021

Speed Up SPICE with a GPU

Circuit designers know that SPICE circuit simulators use a large matrix to simultaneously solve for currents and voltages, taking small enough time steps to ensure convergence and simulation stability. The trouble is that using a general purpose CPU to make these matrix calculations is quite time consuming, meaning that an engineer can wait hours or days to see any simulation results. Since necessity is the mother of all invention, some clever EDA engineers have looked to speed up SPICE circuit simulations by using GPUs.

2.) TinySPICE

3.) with CUSPICE

with CUSPICE 4.) CUDA Circuit Simulator

Apr 7, 2021

[paper] Compact Modeling as a Bridge between Technologies and ICs

Mar 2, 2021

[paper] Predictive Hot-Carrier Aging Compact Model

2Department of Electrical Engineering (ESAT), KU Leuven, Leuven (B)

3Institute for Microelectronics (IuE), TU Wien, Vienna (A)

4Ioffe Physical-Technical Institute of the Russian Academy of Sciences, Saint Petersburg (RU)

5Department of Electronics and Informatics (ETRO/VUB), Brussels (B)

Feb 26, 2021

[DAY 2] 1st Asia/South Pacific MOS-AK Workshop

Day2: FEB.26

Session C Chair: Sadayuki Yoshitomi, Kioxia (J)

[8] eSim: An open source CAD software for circuit simulation

Kannan Moudgalya

IIT Bombay (IN)

[9] A modular approach to next generation Qucs

Felix Salfelder and Mike Brinson

QUCS Team; Centre for Communications Technology, London Metropolitan University (UK)

Tian-Li Wu

National Yang Ming Chiao Tung University, Taiwan (TW)

[11] TCAD-inspired compact modeling approach

Sung-Min Hong and Kwang-Woon Lee

Gwangju GIST (KR)

Session D Chair: Sheikh Aamir Ahsan, NIT Srinagar (IN)

[10] An Innovative Technique for Ultrafast Carrier Dynamics and THz Conductivities of Semiconductor Nanomaterials

Praveen Kr. Saxena and Fanish Kr. Gupta

Tech Next Lab, Lucknow (IN)

Shubham Sahay

IIT Kanpur (IN)

Takayuki Mori and Jiro Ida

Kanazawa Institute of Technology, Nonoichi (J)

[DAY 1] 1st Asia/South Pacific MOS-AK Workshop

DAY 1: FEB. 25, 2021

Session A Chair: Usha Gogineni, ams AG, Hyderabad (IN)

[1] New Insights in Low Frequency Noise Characteristics in PE-BJTs

Peijian Zhang and Ma Long

Science and Technology on Analog Integrated Circuit Laboratory; WHU (CN), Keysight Technologies (US)

[2] Direct white noise characterization of short-channel MOSFETs

K. Ohmori and S. Amakawa

DeviceLab, Tsukuba (J)

[3] SPICE Modeling of 2D-material based FETs with Schottky-barrier contacts

Sheikh Aamir Ahsan

Nanoelectronics Research and Development Group, NIT Srinagar, Jammu and Kashmir (IN)

[4] Physics-based model of SiC MOSFETs including high voltage and current regions

Sourabh Khandelwal, Cristino Salcines, and Ingmar Kallfass

Macquarie University Sydney (AU), University of Stuttgart (D)

Session B Chair: Daniel Tomaszewski, IMiF, Warszaw (PL)

[5] Compact Modeling for Gate-All-Around FET Technology

Avirup Dasgupta

IIT Roorkee (IN)

[6] BSIM-HV: Advanced High Voltage MOSFET Compact Model

Harshit Agarwal

IIT Jodhpur (IN)

[7] ASCENT+ Transnational Access for the nanoelectronics

Georgios Fagas

Tyndall (IE)

Feb 23, 2021

[papers] Compact/SPICE Modeling

[1] Wang, Jie; Chen, Zhanfei; You, Shuzhen; Bakeroot, Benoit; Liu, Jun; Decoutere, Stefaan; "Surface-Potential-Based Compact Modeling of p-GaN Gate HEMTs" Micromachines (2021) 12, no. 2: 199; https://doi.org/10.3390/mi12020199

Abstract: We propose a surface potential (SP)-based compact model of p-GaN gate high electron mobility transistors (HEMTs) which solves the Poisson equation. The model includes all possible charges in the GaN channel layer, including the unintended Mg doping density caused by out-diffusion. The SP equation and its analytical approximate solution provide a high degree of accuracy for the SP calculation, from which the closed-form I–V equations are derived. The proposed model uses physical parameters only and is implemented in Verilog-A code.