Feb 18, 2026

[paper] Compact Modeling of Ferroelectric Devices

Jan 7, 2026

[Data] CMOS SKY130 Cryo Primitives

| Name | File Type | Size |

|---|---|---|

| 2997_README_v4.txt | Plain text | 4.46 kB |

| ETest Tile.zip | Compressed file archive | 3.81 MB |

| MPW-5 Test Tile.zip | Compressed file archive | 39.5 MB |

Dec 14, 2025

[paper] Low-Frequency Noise in Single-Layer Graphene FETs

Departament d’Enginyeria Electrònica, Escola d’Enginyeria, Universitat Autònoma de Barcelona, Bellaterra 08193 (SP)

Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada, 18011 Granada (SP)

Feb 18, 2025

[paper] Benchmarks for SPICE AI/ML Modeling

2 NXP Semiconductors N.V., Eindhoven (NL)

3 NXP Semiconductors N.V., Austin (USA)

4 IIT Kanpur, (IN)

5 TSMC, Hsinchu (TW)

TAB: CHECKLIST FOR MODELS

| Capability | Existing State-of-the-Art | Proposed AI/ML Approach | Best Prior AI/ML Approach |

|---|---|---|---|

| obeys the laws of thermodynamics | ✓ | ? | ? |

| accurate DC modeling for all terminal currents, on relevant log/linear scale | ✓ | ? | ? |

| accurate capacitance/charge modeling | ✓ | ? | ? |

| models DC and capacitance interaction where relevant | ✓ | ? | ? |

| accurate modeling of high-frequency/non-quasi-static effects where relevant | ✓ | ? | ? |

| works for large-signal transient simulation, including delay effects | ✓ | ? | ? |

| accurate noise modeling | ✓ | ? | ? |

| has full geometry dependence | ✓ | ? | ? |

| has complete temperature dependence | ✓ | ? | ? |

| models all necessary LDEs | ✓ | ? | ? |

| behaves “well” for unreasonable geometry or temperature or bias | ✓ | ? | ? |

| exhibits physical monotonicity over bias, geometry, and temperature | ✓ | ? | ? |

| is smooth (ideally C∞-continuous) | ✓ | ? | ? |

| exhibits relevant physical symmetries (currents, charges, their derivatives) | ✓ | ? | ? |

| exhibits asymptotic correctness over geometry, temperature, and bias | ✓ | ? | ? |

| includes modeling of electrothermal effects (with frequency dependence) | ✓ | ? | ? |

| includes, or enables, modeling of global and local statistical variation | ✓ | ? | ? |

| includes, or enables, modeling of aging | ✓ | ? | ? |

| enables modeling of parasitics for different layouts | ✓ | ? | ? |

| is verified to converge reliably in at least one circuit simulator | ✓ | ? | ? |

Dec 26, 2024

[C4P] ICMC 2025

| IMPORTANT DATES

Abstract Submission Deadline January 15, 2025 Acceptance Notifications March 10, 2025 Full Paper Submission Deadline April 20, 2025 ORGANIZING COMMITTEE General Chair Peter M. Lee Micron Vice Chair Shahed Reza Sandia Lab Technical Program Chair Colin Shaw Silvaco Technical Program Vice Chair Gert-Jan Smit NXP Treasurer Leigh Anne Clevenger Si2 Secretariat Conference Catalysts icmc@conferencecatalysts.com  |

The Compact Model Coalition (CMC) brings academia and industry partners together in the development and standardization of compact models for semiconductor devices. For 30 years now, the CMC has been instrumental in creating standardized and verified models for designers to use in their increasingly complex circuits for SPICE simulation. The CMC is organizing a new and innovative International Compact Modeling Conference. Cosponsored by IEEE EDS, it will focus uniquely on compact device models, their development and broad application in the semiconductor industry. You are invited to participate in the evolution of these models, guide model development to help circuit designers create the best circuit performance possible, and enable foundries to leverage the strength of their device fabrication to full extent. Join the world experts in design, process technology, and model development to discuss state-of-the-art semiconductor device modeling for a two-day in-person event in one location, offering a great opportunity to present and learn about this core element of circuit design and how to get the most from these global collaborations. We are seeking papers for oral or poster presentations in the following areas: APPLICATION OF DEVICE MODELS

Please submit your paper proposals in the form of a 2-page abstract for review by

January 15, 2025 here 2025.si2-icmc.org. Acceptance notifications will be sent by

March 10, 2025. Accepted contributions (for both oral and poster presentations) are

expected to submit a camera-ready 4-page draft version of their papers by April 20,

2025 and final version by May 23, 2025 for publication in IEEE Xplore®. |

Oct 28, 2024

[paper] FOSS support for CM with Verilog-A

Apr 26, 2024

[paper] Compact Modeling of Hysteresis in OTFTs

a Departamento de Electrónica y Tecnología de Computadores, CITIC-UGR, Uni Granada, Spain

b Department of Industrial Engineering and Construction, Universitat de les Illes Balears, Spain

c Department of Electrical and Computer Engineering, McMaster University, Canada

Jan 11, 2024

[paper] Neural Compact Modeling Framework

Abstract: Neural compact models are proposed to simplify device-modeling processes without requiring domain expertise. However, the existing models have certain limitations. Specifically, some models are not parameterized, while others compromise accuracy and speed, which limits their usefulness in multi-device applications and reduces the quality of circuit simulations. To address these drawbacks, a neural compact modeling framework with a flexible selection of technology-based model parameters using a two-stage neural network (NN) architecture is proposed. The proposed neural compact model comprises two NN components: one utilizes model parameters to program the other, which can then describe the current–voltage (IV) characteristics of the device. Unlike previous neural compact models, this two-stage network structure enables high accuracy and fast simulation program with integrated circuit emphasis (SPICE) simulation without any trade-off. The IV characteristics of 1000 amorphous indium–gallium–zinc-oxide thin-film transistor devices with different properties obtained through fully calibrated technology computer-aided design simulations are utilized to train and test the model and a highly precise neural compact model with an average IDS error of 0.27% and R2 DC characteristic values above 0.995 is acquired. Moreover, the proposed framework outperforms the previous neural compact modeling methods in terms of SPICE simulation speed, training speed, and accuracy.

Nov 2, 2023

[paper] Surface-Potential-Based Compact Modeling

Oct 6, 2023

[book chapters] Equation-Based Compact Modeling

Chapter: Differential Equation-Based Compact 2-D Modeling of Asymmetric Gate Oxide Heterojunction Tunnel FET; By: Sudipta Ghosh, Arghyadeep Sarkar

Abstract: Tunnel Field Effect Transistor (TFET) has emerged as an effective alternative device to replace MOSFET for a few decades. The major drawbacks of MOSFET devices are the short-channel effects, due to which the leakage current increases with a decrease in device dimension. So, scaling down TFET is more efficacious than that of MOSFETs. Sub-threshold swing (SS) is another advantageous characteristic of TFET devices for high-speed digital applications. In TFETs the SS could be well below 60 mV/decade, which is the thermal limit for MOSFET devices and therefore makes it more suitable than MOSFET for faster switching applications. It is observed from the literature studies that the performances of the TFET devices have been explored thoroughly by using 2-D TCAD simulation but an analytical model is always essential to understand the physical behavior of the device and the physics behind this; which facilitates further, the analysis of the device performances at circuit level as and when implemented.Chapter: Differential Equation-Based Analytical Modeling of the Characteristics Parameters of the Junctionless MOSFET-Based Label-Free Biosensors; by: Manash Chanda, Papiya Debnath, Avtar Singh

Abstract: Recently Field Effect transistor (FET)-based biosensing applications have gained significant attention due to the demand for quick and accurate diagnosis of different enzymes, proteins, DNA, viruses, etc; cost-effective fabrication process; portability and better sensitivity and selectivity compared to the existing biosensors. FET is basically a three-terminal device with source, drain, and gate terminals. Basically, the gate terminal controls the current flow between the source and drain terminals. In FETs, first, a nanogap is created in the oxide layer or in the gate by etching adequate materials. When the biomolecules are trapped inside the nanocavity then the surface potentials change and also the threshold voltage varies. As a result, the output current also changes. Finally, by measuring the changes in the threshold voltage or the device current, one can easily detect the biomolecules easily.

May 23, 2023

[paper] Schottky Barrier FET at Deep Cryogenic Temperatures

1 NanoP, TH Mittelhessen - University of Applied Sciences, Giessen, Germany

2 DEEEA, Universitat Rovira i Virgili, Tarragona, Spain

3 Peter-Grunberg-Institute (PGI 9), Forschungszentrum Julich, Germany

Apr 18, 2023

Compact Modeling of 2D Field-Effect Biosensors

1 Pervasive Electronics Advanced Research Laboratory (PEARL), Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada,18071 Granada, Spain

2 Laboratory of Physics of Materials and Nanomaterials Applied at Environment (LaPhyMNE) LR05ES14, Faculty of Sciences of Gabes, Gabes University, Erriadh City, Zrig, 6072 Gabes, Tunisia

Mar 22, 2023

[analog-wg] Video of March 21 AWG Meeting

The AWG Video Meeting on March 21, 2023 included two presentations:

- Ken Kundert "Why Fund OpenVAF"

- Pascal Kuthe "OpenVAF: An innovative open-source Verilog-A Compiler"

|

|

|

- 4th April: Update from Tim Edwards: Magic and PEX extraction

- 18th April: Update from Sadayuki Yoshitomi: Ecosystem of compact model development

- 2nd May (tentative): Update from C. Enz,EPFL: test structures measurements

Jan 18, 2023

Neural networks and machine learning approach for compact modeling

Highlights

- The cryogenic characterization of SMIC CMOS technology at 4.2K is presented.

- An optimization model VCCS is proposed to calibrate the cryogenic characteristics.

- BP neural network is, for the first time, used in MOSFET modeling.

- The cryo-model can be applied to SPICE simulator and assist in cryo-CMOS circuit design and simulation.

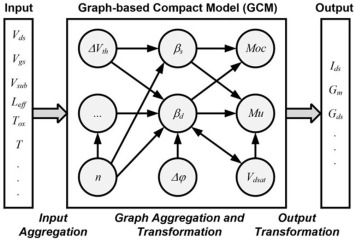

- Developed a Graph-based compact model for FinFET.

- Model implemented in Verilog-A for SPICE simulation.

- Requires less number of model parameters and is computationally efficient than BSIM

Apr 26, 2022

[paper] Universal Charge Model for Multigate MOS Structures

Jan 12, 2022

[paper] Compact Modelling of Si Nanowire/Nanosheet MOSFETs

2 Centro Universitario PEI, Sao Bernardo do Cainpo, Sao Paulo, Brazil

Nov 9, 2021

8th EuroSOI-ULIS 2022 at University of Udine (Italy)

| Organized

by:

University of Udine (Italy) Conference chair: Pierpaolo Palestri Local organizing Committee: Francesco Driussi Conference Secretariat: Centro Congressi Internazionali Steering Committee:

|

8th Joint

International EuroSOI Workshop and International Conference on Ultimate Integration on Silicon (EuroSOI-ULIS) 2022 May 18-20, 2022 – Udine, Italy https://eurosoiulis2022.com The Conference aims at gathering

together scientists and engineers working in academia, research centers

and industry in the field of SOI technology and nanoscale devices in

More-Moore and More-Than-Moore scenarios. High quality contributions in the following areas are

solicited:

Original 2-page abstracts with

illustrations will be reviewed by the Scientific Committee. The

accepted contributions will be published as 4-page letters in a special

issue of the Elsevier journal Solid-State Electronics.

Extended versions of outstanding papers will be published in a further

special issue of Solid-State Electronics. A best poster award will be

attributed by ELSEVIER.

The “Androula

Nassiopoulou Best Paper Award" will be attributed by the

SINANO institute.

Important dates:

|

Oct 20, 2021

[paper] Parameter Extraction Approaches for Memristor Models

1 Moscow Institute of Physics and Technology, Moscow, Russia;

2 JSС MERI, Zelenograd, Russia

Abstract: Memristors are among the most promising devices for building neural processors and non-volatile memory. One circuit design stage involves modeling, which includes the option of memristor models. The most common approach is the use of compact models, the accuracy of which is often determined by the accuracy of their parameter extraction from experiment results. In this paper, a review of existing extraction methods was performed and new parameter extraction algorithms for an adaptive compact model were proposed. The effectiveness of the developed methods was confirmed for the volt-ampere characteristic of a memristor with a vertical structure: TiN/HfxAl1-xOy/HfO2/TiN.

Oct 7, 2021

[paper] Compact Schottky-barrier CNTFET Modeling

CEDIC, Technische Universität Dresden (D)

Aug 7, 2021

[paper] Compact Model for Thin-Film Heterojunction Anti-Ambipolar Transistors

* Department of Electronic Engineering, Gachon University, Seongnam 13120, South Korea