Tapas Dutta, Fikru Adamu-Lema, Djamel Bensouiah, German Cherstvov, Plamen Asenov,

and Asen Asenov

FDSOI Based Cryogenic Circuit Performance Enhancement

Using Back Biasing and Threshold Voltage Engineering

IEEE Journal of the Electron Devices Society (2026)

DOI 10.1109/JEDS.2026.3691285

Pramana Modelling Labs, Glasgow, UK

School of Engineering, University of Glasgow, UK

Semiwise Ltd., Glasgow, UK

Synopsys, Glasgow, UK

Abstract

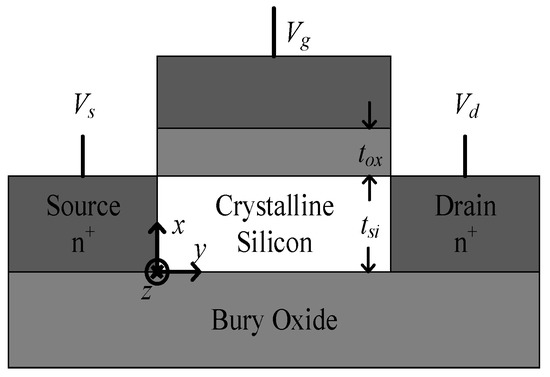

: In this work, we use predictive cryogenic spice based compact models derived using a process design kit re-centering approach for 22 nm FDSOI technology to analyze the impact of back-gate biasing on circuit performance. We focus on analysis of power-delay trade-offs while varying the supply voltage at room and cryogenic temperature (4K). We show that back-biasing is necessary to mitigate the effects of the higher threshold voltages observed at cryogenic temperature. We further show that simple “threshold voltage engineering” has the potential to provide much better performance, compared to room temperature.

Fig

: IDS −VGS characteristics for different VBG going to much higher values

than the previous sections (without applying anyVth shift).

Acknowledgement

: We are grateful to GlobalFoundries for providing the 22FDX PDK and allowing us to customize it for cryogenic temperature operation. The device measurements were performed by Incize SRL, Belgium. This work was supported partially by Innovate UK funded project “Development of Cryo-CMOS to enable the next generation of scalable quantum computers” under the grant number of 10006017 and was also partially supported by Semiwise Ltd, UK.