Nanoscale MOSFET Modeling:

Part 1: The Simplified EKV Model for the Design of Low-Power Analog Circuits

C. Enz, F. Chicco and A. Pezzotta

in IEEE Solid-State Circuits Magazine, vol. 9, no. 3, pp. 26-35, Summer 2017

doi: 10.1109/MSSC.2017.2712318

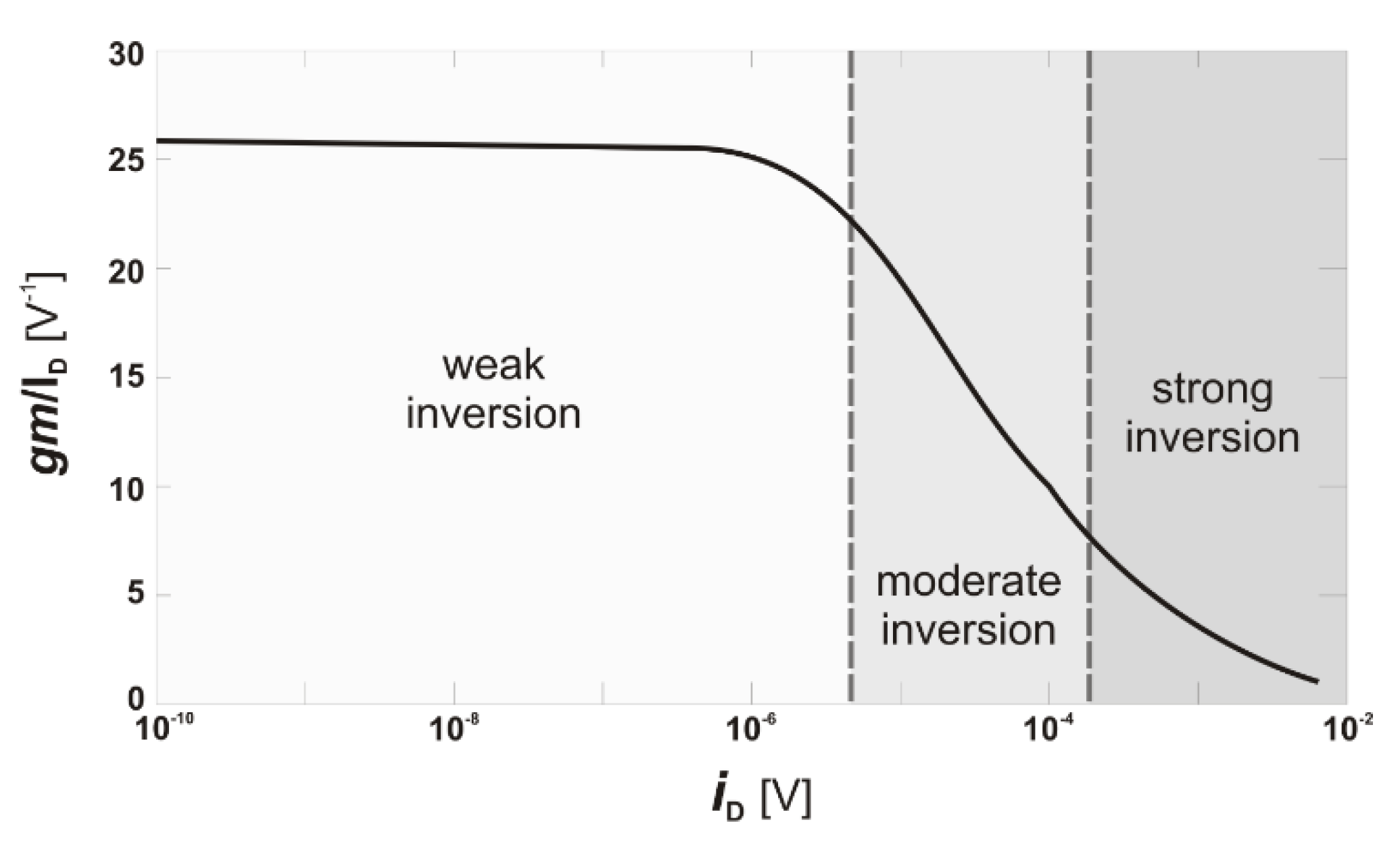

Abstract: This article presents the simplified charge-based Enz-Krummenacher-Vittoz (

EKV) [11] metal-oxide-semiconductor field-effect transistor (MOSFET) model and shows that it can be used for advanced complementary metal-oxide-semiconductor (CMOS) processes despite its very few parameters. The concept of an inversion coefficient (

IC) is first introduced as an essential design parameter that replaces the overdrive voltage V

G-V

T0 and spans the entire range of operating points from weak via moderate to strong inversion (

SI), including the effect of velocity saturation (

VS). The simplified model in saturation is then presented and validated for different 40- and 28-nm bulk CMOS processes. A very simple expression of the normalized transconductance in saturation, valid from weak to

SI and requiring only the

VS parameter

mc, is described. The normalized transconductance efficiency

Gm/ID, which is a key figure-of-merit (FoM) for the design of low-power analog circuits, is then derived as a function of

IC including the effect of

VS. It is then successfully validated from weak to

SI with data measured on a 40-nm and two 28-nm bulk CMOS processes. It is then shown that the normalized output conductance

Gds/ID follows a similar dependence with

IC than the normalized

Gm/ID characteristic but with different parameters accounting for drain induced barrier lowering (DIBL). The methodology for extracting the few parameters from the measured

ID-VG and

ID-VD characteristics is then detailed. Finally, it is shown that the simplified

EKV model can also be used for a fully depleted silicon on insulator (FDSOI) and Fin-FET 28-nm processes [

read more...]

FIG: The simplified EKV model applied to a 28-nm FDSOI CMOS process:

Gm n UT / ID versus IC for three different transistor channel lengths

References

[1] A. Bahai, “Ultra-low energy systems: Analog to information,” in Proc. European Solid-State Circ. Conf., Sept. 2016, pp. 3–6.

[2] D. Binkley, Tradeoffs and Optimization in Analog CMOS Design. Hoboken, NJ: Wiley, 2008.

[3] W. Sansen, Analog Design Essentials. New York: Springer-Verlag, 2006.

[4] A. Mangla, M. A. Chalkiadaki, F. Fadhuile, T. Taris, Y. Deval, and C. C. Enz, “Design methodology for ultra low-power analog circuits using next generation BSIM6 MOSFET compact model,” Microelectr. J., vol. 44, no. 7, pp. 570–575, July 2013.

[5] Y. S. Chauhan, S. Venugopalan, M. A. Chalkiadaki, M. A. U. Karim, H. Agarwal, S. Khandelwal, N. Paydavosi, J. P. Duarte, C. C. Enz, A. M. Niknejad, and C. Hu, “BSIM6: Analog and RF compact model for bulk MOSFET,” IEEE Trans. Electron Dev., vol. 61, no. 2, pp. 234–244, Feb. 2014.

[6] C. Enz, M. A. Chalkiadaki, and A. Mangla, “Low-power analog/RF circuit design based on the inversion coefficient,” in Proc. European Solid-State Circ. Conf., Sept. 2015, pp. 202–208.

[7] C. Enz and A. Pezzotta, “Nanoscale MOSFET modeling for the design of low-power analog and RF circuits,” in Proc. Int. Conf. MIXDES, June 2016, pp. 21–26.

[8] W. Sansen, “Analog CMOS from 5 micrometer to 5 nanometer,” in Proc. IEEE Int. Solid State Circuits Conf. Dig. Tech. Papers, Feb. 2015, pp. 1–6.

[9] W. Sansen, “Analog design procedures for channel lengths down to 20 nm,” in Proc. IEEE 20th Int. Conf. Electronics, Circuits, and Systems, Dec. 2013, pp. 337–340.

[10] C. C. Enz and E. A. Vittoz, Charge-Based MOS Transistor Modeling - The EKV Model for Low-Power and RF IC Design. Hoboken, NJ: Wiley, 2006.

[11] C. C. Enz, F. Krummenacher, and E. A. Vittoz, “An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications,” Analog Integr. Circuits Signal Process. J., vol. 8, pp. 83–114, July 1995.

[12] P. Heim, S. R. Schultz, and M. A. Jabri, “Technology-independent biasing technique for CMOS analogue micropower implementations of neural networks,” in Proc. Sixth Australian Conf. Neural Networks, Sydney, Australia, 1995, pp. 9–12.

[13] C. C. Enz and E. A. Vittoz, “CMOS low-power analog circuit design,” in EmergingTechnologies: Designing Low Power Digital Systems, R. Cavin and W. Liu, Eds. Piscataway, NJ: IEEE, 1996, pp. 79–133.

[14] E. Vittoz and J. Fellrath, “CMOS analog integrated circuits based on weak inversion operations,” IEEE J. Solid-State Circuits, vol. 12, no. 3, pp. 224–231, June 1977.

[15] A. Mangla, C. C. Enz, and J. M. Sallese, “Figure-of-merit for optimizing the current efficiency of low-power RF circuits,” in Proc. Int. Conf. Mixed Design Integrated Circuits and Systems, June 2011, pp. 85–89.

[16] A. Mangla, “Modeling nanoscale quasi-ballistic MOS transistors,” Ph.D. dissertation, EPFL, Switzerland, Dissertation No. 6385, 2014.

[17] R. R. Troutman and A. G. Fortino, “Simple model for threshold voltage in a short- channel IGFET,” IEEE Trans. Electron. Dev., vol. 24, no. 10, pp. 1266–1268, Oct. 1977.

[18] N. Arora, MOSFET Models for VLSI Circuit Simulation. New York: Springer-Verlag, 1993.

[19] Z. H. Liu, C. Hu, J. H. Huang, T. Y. Chan, M. C. Jeng, P. K. Ko, and Y. C. Cheng, “Threshold voltage model for deep submicrometer MOSFETs,” IEEE Trans. Electron Dev., vol. 40, no. 1, pp. 86–95, Jan. 1993.

[20] M. A. Chalkiadaki, “Characterization and modeling of nanoscale MOSFET for ultra-low power RF IC design,” Ph.D. dissertation, EPFL, Switzerland, Dissertation No. 7030, 2016.