Abstract: Neural compact models are proposed to simplify device-modeling processes without requiring domain expertise. However, the existing models have certain limitations. Specifically, some models are not parameterized, while others compromise accuracy and speed, which limits their usefulness in multi-device applications and reduces the quality of circuit simulations. To address these drawbacks, a neural compact modeling framework with a flexible selection of technology-based model parameters using a two-stage neural network (NN) architecture is proposed. The proposed neural compact model comprises two NN components: one utilizes model parameters to program the other, which can then describe the current–voltage (IV) characteristics of the device. Unlike previous neural compact models, this two-stage network structure enables high accuracy and fast simulation program with integrated circuit emphasis (SPICE) simulation without any trade-off. The IV characteristics of 1000 amorphous indium–gallium–zinc-oxide thin-film transistor devices with different properties obtained through fully calibrated technology computer-aided design simulations are utilized to train and test the model and a highly precise neural compact model with an average IDS error of 0.27% and R2 DC characteristic values above 0.995 is acquired. Moreover, the proposed framework outperforms the previous neural compact modeling methods in terms of SPICE simulation speed, training speed, and accuracy.

Showing posts with label Framework. Show all posts

Showing posts with label Framework. Show all posts

Jan 11, 2024

[paper] Neural Compact Modeling Framework

Eom, Seungjoon, Hyeok Yun, Hyundong Jang, Kyeongrae Cho, Seunghwan Lee, Jinsu Jeong, and Rock‐Hyun Baek

Neural Compact Modeling Framework for Flexible Model Parameter Selection with High Accuracy and Fast SPICE Simulation

Advanced Intelligent Systems (2023): 2300435

DOI: 10.1002/aisy.202300435

Department of Electrical Engineering, Pohang University of Science and Technology, Pohang 37673 (KR)

Fig: a) The structure of a-IGZO TFT structure simulated with TCAD

b) Calibrated a-IGZO sub-gap DOS

Acknowledgements: This work was supported in part by the LG Display Company, in part by the Brain Korea 21 Fostering Outstanding Universities for Research (BK21 FOUR) program, in part by Institute of Information and Communications Technology Planning and Evaluation (IITP) grant funded by the Korea government (MSIT) (grant no. 2019-0-01906, Artificial Intelligence Graduate School Program [POSTECH]), in part by the Ministry of Trade, Industry and Energy (MOTIE) under grant no. 20020265, in part by Korea Semiconductor Research Consortium (KSRC) support program for the development of the future semiconductor device, and in part by the Technology Innovation Program (grant no. RS2023-00231985) funded by the Ministry of Trade, Industry and Energy (MOTIE, Korea) (grant no. 1415187390).

Jul 13, 2021

[paper] ML based Aging-Aware FPGA Framework

Behnam Ghavami, Milad Ibrahimipour, Zhenman Fang, Lesley Shannon

MAPLE: A Machine Learning based Aging-Aware FPGA Architecture Exploration Framework

31st International Conference on Field-Programmable Logic and Applications

(FPL 2021 Short Paper),

Virtual Conference, Sept 2021

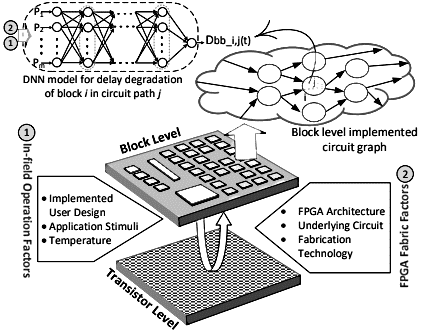

*Simon Fraser University, Burnaby, BC, CanadaAbstract: In this paper, we develop a framework called MAPLE to enable the aging-aware FPGA architecture exploration. The core idea is to efficiently model the aging-induced delay degradation at the coarse-grained FPGA basic block level using deep neural networks (DNNs). For each type of the FPGA basic block such as LUT and DSP, we first characterize its accurate delay degradation via transistor-level SPICE simulation under a versatile set of aging factors from the FPGA fabric and in-field operation. Then we train one DNN model for each block type to quickly and accurately predict the complex relation between its delay degradation and comprehensive aging factors. Moreover, we integrate our DNN models into the widely used Verilog-to-Routing toolflow (VTR 8) to support analyzing the impact of aging-induced delay degradation on the entire large scale FPGA architecture. Experimental results demonstrate that MAPLE can predict the delay degradation of FPGA blocks 104 to 107 times faster than transistor-level SPICE simulation, with a prediction error less than 0.7%. Our case study demonstrates that FPGA architects can effectively leverage MAPLE to explore better aging-aware FPGA architectures.

Fig: Overview of FPGA fabric and in-field factors affecting FPGA aging at transistor and basic block levels. We use DNNs to model FPGA delay degradation at basic block level.

Acknowledgements: We acknowledge the support from Government of Canada Technology Demonstration Program and MDA Systems Ltd; NSERC Discovery Grant RGPIN-2019-04613 and DGECR 2019-00120; Canada Foundation for Innovation John R. Evans Leaders Fund; Simon Fraser University New Faculty Start-up Grant; Xilinx, Huawei and Nvidia.

Subscribe to:

Comments (Atom)