(read further *Contributors include Tom Waldrop and Intel Communications)

Mar 29, 2023

In Menoriam: Gordon Moore, 1929 - 2023

(read further *Contributors include Tom Waldrop and Intel Communications)

[paper] Extraction and Automated FEMM Creation of a Transformer SPICE Model

*Advent Technologies A/S Lyngvej 8, Aalborg, 9000, Denmark e-mail: denys.zaikin@advent.energy

[Deadline Extended] IEEE LAEDC 2023

|

Mar 24, 2023

Thirteen regions of #EU have come together to form a #semi #alliance https://t.co/T655QCutbq https://t.co/l37dp4pHqI

Thirteen regions of #EU have come together to form a #semi #alliance https://t.co/T655QCutbq https://t.co/l37dp4pHqI

— Wladek Grabinski (@wladek60) Mar 24, 2023

from Twitter https://twitter.com/wladek60

March 24, 2023 at 01:18PM

via IFTTT

Mar 22, 2023

[analog-wg] Video of March 21 AWG Meeting

The AWG Video Meeting on March 21, 2023 included two presentations:

- Ken Kundert "Why Fund OpenVAF"

- Pascal Kuthe "OpenVAF: An innovative open-source Verilog-A Compiler"

|

|

|

- 4th April: Update from Tim Edwards: Magic and PEX extraction

- 18th April: Update from Sadayuki Yoshitomi: Ecosystem of compact model development

- 2nd May (tentative): Update from C. Enz,EPFL: test structures measurements

Mar 21, 2023

Commemorative and Networking Event: 75th anniversary of the transistor

Three IEEE Distinguished Lecturers will talk about the transistor history and its properties. It will be followed by short presentations about semiconductor industry activities in Switzerland, with the following networking apéro.

Attendance is free and open to all: mention it and forward to your friends and colleagues.

Please register for logistics reasons.

Date and Time |

Location |

|---|---|

|

|

Agenda

13:00 – 13:30 Welcome Coffee

13:30 – 14:15 Tom Lee: From Rocks to Chips: Stories of the Transistor

14:15 – 15:15 Chris Mangelsdorf: Don't try this with CMOS

15:15 – 15:45 Coffee break

15:45 – 16:30 Christian Enz: The Design of Low-power Analog CMOS Circuits Using the Inversion Coefficient

16:30 – 17:30 Semiconductor industry in Switzerland, sharing experiences

(W.Grabinski, Panel Moderator):

- Bipolar transistor manufacturing in Switzerland – Hugo Wyss

- Integrated Circuits – Eric Vittoz

- Semiconductor design in the 21st century – Alain-Serge Poret

- Micro-electronics for Swiss made products – Evert Dijkstra

- Semiconductor manufacturing equipment – André Gerde

17:30 – 19:00 Apéro riche

Hosts

Switzerland Section Chapter, SSC37 : https://sscs.ieee.chSwitzerland Section : https://ieee.ch/

Mar 17, 2023

Silicon Chip Industry Awareness Seminar

Silicon Chip Industry Awareness Workshop Seminar

Whether you're a non-technologist struggling with the jargon or a specialist looking to understand the overall industry structure, this workshop is for you. Join us on Tue 28 March 2023, 9:30am to 4:00pm at the Holiday Inn in Kensington, London, England. Gain a competitive edge in the Semiconductor Industry by learning how the IC industry works from the science that enables silicon chips to be made from sand to the market fundamentals that drive applications and economics. Experience the industry through Listen, Discuss, See, Touch, and Learn activities and enjoy improved job satisfaction and operational efficiency.

Priced at just UK£695 plus 20 percent UK VAT per delegate, the fee includes copies of presentation materials, coffee breaks and lunch. Workshops can also be held in-house for your added convenience and flexibility. Only 10 spots available, so don't wait – Secure Your Spot Today at: https://www.futurehorizons.com/page/12/silicon-chip-training

Past Attendee Comments

* As a non-technologist, it was very beneficial to have these issues so clearly explained

* The seminar provided a good basis to understanding the industry

* It was GREAT! I can't remember a day of a similar density

* I finally understand how to recognize products & their use in technology

* This has helped me structure my thoughts & plans for the company

* It gave me deeper insight into the industry in a way difficult to obtain anywhere else

* This will be very useful when involved in our core business development discussions

Please pass to your HR Department or a colleague if already attended or not suitable for you.

Sincerely

Malcolm Penn, Chairman & CEO

Blakes Green Cottage, Sevenoaks, Kent TN15 0LQ, England

Tel: +44 (0)1732 740440

Registered Company: 4380991

Follow us on Twitter @Future_Horizons

and join our Linked In Group (http://uk.linkedin.com/in/malcolmpenn)

and receive regular industry news, information and comments.

#7nm #OpenROAD Design Contest

[@Anagha_Ghosh] Recap of the Successful #7nm #OpenROAD Design Contest Launch #semi #desing #opensource https://t.co/wDVcDJUiBo

— Wladek Grabinski (@wladek60) Mar 17, 2023

from Twitter https://twitter.com/wladek60

March 17, 2023 at 08:47AM

via IFTTT

Mar 16, 2023

How new #semi fabrication #chip will power #India towards growth

How new #semi fabrication #chip will power #India towards growth https://t.co/vNDBzpKH2c https://t.co/ajD2brWt1D

— Wladek Grabinski (@wladek60) Mar 16, 2023

from Twitter https://twitter.com/wladek60

March 16, 2023 at 03:18PM

via IFTTT

Mar 15, 2023

#Samsung to invest in South Korea

#Samsung to invest in South Korea #mega #semi chip-making #plan https://t.co/ryMYKRclVi https://t.co/VaLanWwUST

— Wladek Grabinski (@wladek60) Mar 15, 2023

from Twitter https://twitter.com/wladek60

March 15, 2023 at 08:28PM

via IFTTT

First Indian #semi #fab will be declared in a few weeks

[https://t.co/qtxGLqhZm8] First #semi #fab will be declared in a few weeks: IT Minister Ashwini Vaishnaw https://t.co/x5Gcp9BMVR https://t.co/eHZLSL12Y0

— Wladek Grabinski (@wladek60) Mar 15, 2023

from Twitter https://twitter.com/wladek60

March 15, 2023 at 04:42PM

via IFTTT

[paper] Noise Characterization of MOSFETs for Cryogenic Electronics

[paper] highly segmented hybrid pixel detectors

I. Kremastiotisa, X. Lloparta, M. Noya, A. Paternoa, M. Pillera g, J.M. Sallesseh, V. Sriskarana,

L. Tlustosa c, M. van Beuzekomf

a CERN, Experimental Physics Department, Meyrin, 1211, Switzerland

b SLAC National Accelerator Laboratory, Menlo Park, 94025, CA, United States

c IEAP, Czech Technical University in Prague, Prague, 11000, Czech Republic

d Department of Biomedical technology, Faculty of Biomedical Engineering, Czech Technical University in Prague, nam. Sitna 3105, Kladno, 272 01, Czech Republic

e KIT - Karlsruhe Institute of Technology, Institute for Data Processing and Electronics (IPE), Hermann-von-Helmholtz-Platz 1, Eggenstein-Leopoldshafen, 76344, Germany

f Nikhef, Science Park 105, Amsterdam, 1098, Netherlands

g Institute of Electronics, Graz University of Technology, Graz, 8010, Austria

h Electron Device Modeling and Technology Laboratory (EDLAB), EPFL, Switzerland

Mar 14, 2023

IEEE CASS IIT Roorkee offline Workshop on Robust and Reliable VLSI Circuits Design

IEEE CASS SBC IIT Roorkee in collaboration with IEEE UP Section and some industry partners is organizing a workshop entitled "Robust and Reliable VLSI Circuits". This is a three-day residential workshop to learn the aspects of reliable and robust design in VLSI circuits from the leading academic/industrial experts.

The benefits of this workshop to the participants will be multifold:

Participants will get an opportunity to interact with leading researchers both from academic and the industry.

Participants will get hand-on experience on various EDA tools.

The participants will get the opportunity to present their recent domain work to the experts.

For Registration click here

To know more visit the R2VC website at

Date: 7-9 April, 2023

Venue: Indian Institute of Technology(IIT) Roorkee,

Uttarakhand

Send you queries at -

Contact us at-

Neha Gupta

9719749045

Kartikay Mani Tripathi

9810938752

Mar 13, 2023

#semiconductors #India #US #innovation

#semiconductors #IndiaUS #innovation #supplychain #semi https://t.co/0FiCjCUg8X

— Wladek Grabinski (@wladek60) Mar 13, 2023

from Twitter https://twitter.com/wladek60

March 13, 2023 at 09:56AM

via IFTTT

Mar 12, 2023

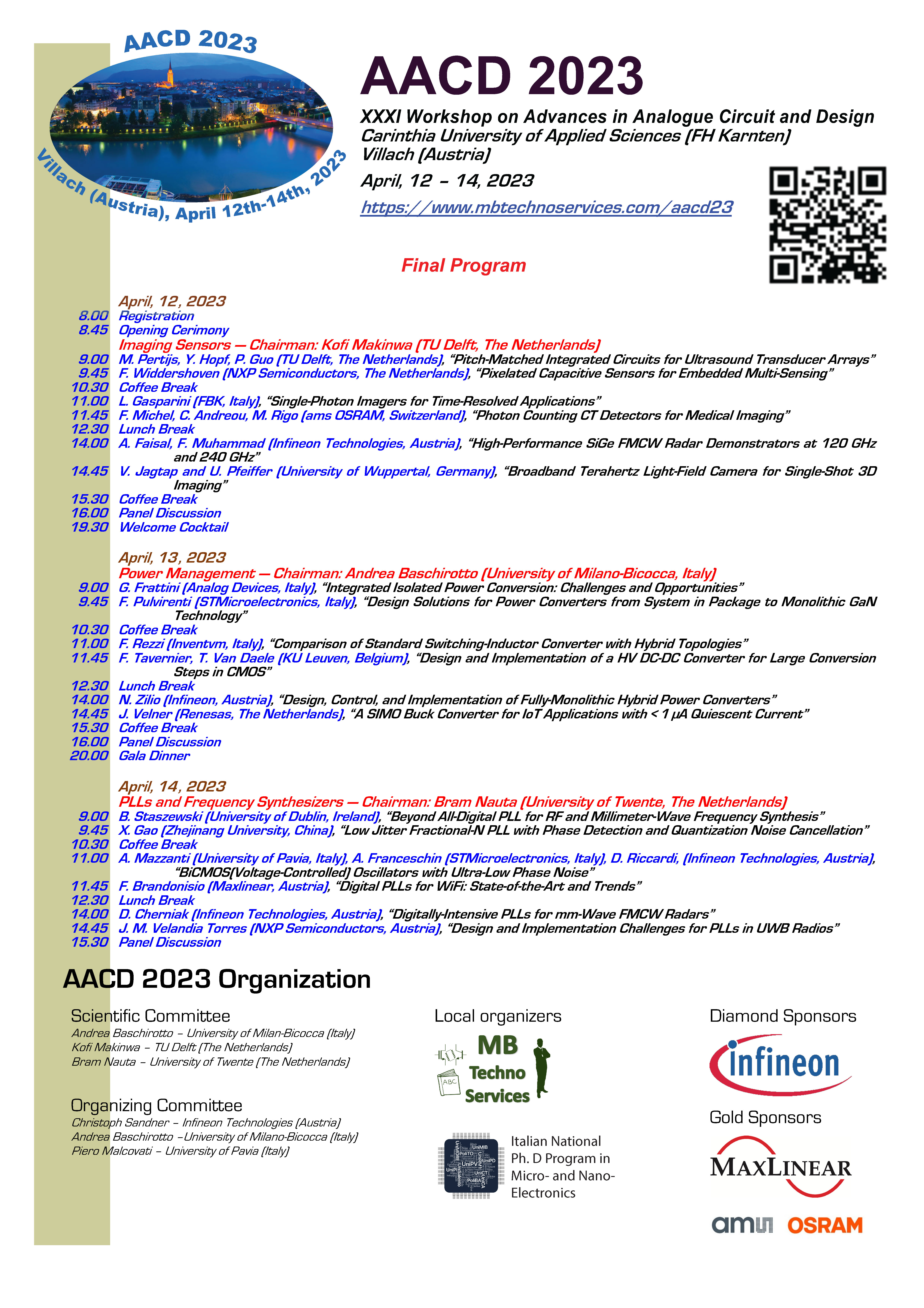

AACD 2023 --- Final Program

Early-bird discounted registration is available till March 19th 2023.

Workshop Registration includes participation to the sessions, pdf documentation, lunches and coffee breaks for the three days, Welcome Cocktail (on April, 12th) and Gala Dinner (on April, 13th).

For any further information:

- Visit http://www.mbtechnoservices.com/aacd23

- Contact AACD23 General Chairman, prof. Andrea Baschirotto (andrea.baschirotto@unimib.it)

We look forward to meeting you in Villach!!!!

Andrea Baschirotto

AACD23 General Chairman

Mar 10, 2023

Hello world in #electornics https://t.co/xXWbkqxlen #semi [https://t.co/CYopGZA4rp] Congratulations, you are now an electrical engineer! 😀 https://t.co/eUc1iStenR

Hello world in #electornics https://t.co/xXWbkqxlen #semi [https://t.co/CYopGZA4rp] Congratulations, you are now an electrical engineer! 😀 https://t.co/eUc1iStenR

— Wladek Grabinski (@wladek60) Mar 10, 2023

from Twitter https://twitter.com/wladek60

March 10, 2023 at 09:11PM

via IFTTT

Mar 8, 2023

[paper] Cryogenic Characteristics of InGaAs MOSFET

Mar 6, 2023

[open position] IHP Research Associate for Open PDK Development

The position:

Your profile:

Your application:

Have we sparked your interest? Then we look forward to receiving your application via our online application form. For further information regarding the position, please contact Dr. René Scholz

[NIST Report] 7 Grand #Challenges for #US #chip industry

[NIST Report] 7 Grand #Challenges for #US #chip industry https://t.co/ZyDfybYgVl #semi https://t.co/OvRMXCIAaZ

— Wladek Grabinski (@wladek60) Mar 6, 2023

from Twitter https://twitter.com/wladek60

March 06, 2023 at 08:54AM

via IFTTT

Mar 3, 2023

[C4P] SEMINATEC 2023

SEMINATEC 2023 Call for Papers

SEMINATEC 2023 will be held at the Institute of Physics Gleb Wataghin, IFGW, auditorium between March 29-31, 2023 as a continuation of previous workshops, all focused on technology trends in the areas of micro and nanotechnology. The goal of this event is to promote the interaction among industry, academy, research & development centers, government and students, all looking for real opportunities towards improving education, research, and technology.

Contributed papers will be selected based on submitted abstracts (up to two pages) in A4 format. Electronic submissions will only be accepted in pdf format and must be submitted prior to March 6, 2023. The notification of acceptance will be on March 12, 2023.

The XVII SEMINATEC welcomes the submission of original papers in all areas related to

- Optoelectronic devices

- Optics and Photonic IC’s

- Fabrication of micro & nano-structures

- Microsystems

- Devices modeling and characterization

- Integrated circuits: design and testing

- CAD and simulation

Abstract Submission (To download the template, click here ) Abstracts will be accepted in PDF format. Please fill the form below and upload your file. All fields required.

SEMINATEC is organized by the School of Electrical and Computer Engineering (FEEC), the Institute of Physics Gleb Wataghin (IFGW) and the Center for Semiconductors Components and Nanotechnologies (CCSNano) at the University of Campinas (UNICAMP), by the Integrated Systems Laboratory (LSI) at the University of São Paulo (USP) and by the Department of Electrical Engineering at FEI, with support/funding from the IEEE Electron Device Society (EDS) South Brazil Chapter, the EDS Student Chapter of UNICAMP and FEI and by the SSCS South Brazil Chapter. The event is also supported by INCT’s NAMITEC, SBMICRO, FAPESP’s Integrated Photonics Devices (iPhD) and Integrated Photonics Lab (LIF SISFOTON).

[Naveed Sherwani] view on ChipAct team needs

From our [Naveed Sherwani] point of view, what ChipAct team needs - sincere advise on deep technical issues from #semi experts. https://t.co/BNUjnLpq5f https://t.co/9mr8vJWiWD

— Wladek Grabinski (@wladek60) Mar 3, 2023

from Twitter https://twitter.com/wladek60

March 03, 2023 at 09:57AM

via IFTTT

Mar 2, 2023

#Apple doubles its $1 billion investment in #German

#Apple doubles its $1 billion investment in #German R&D [AppleInsider https://t.co/Z4P2EMfv2G] #semi https://t.co/T1hNA4q0jU

— Wladek Grabinski (@wladek60) Mar 2, 2023

from Twitter https://twitter.com/wladek60

March 02, 2023 at 02:05PM

via IFTTT

#Yangtze #Memory to get another $1.9bn from #China government

#Yangtze #Memory to get another $1.9bn from #China government https://t.co/15Lfj29aHx #semi https://t.co/Lv5OiwxGf6

— Wladek Grabinski (@wladek60) Mar 2, 2023

from Twitter https://twitter.com/wladek60

March 02, 2023 at 01:55PM

via IFTTT

Add Event to Calendar

Add Event to Calendar