Giovani Britton1,2, Salvador Mir2, Estelle Lauga-Larroze2, Benjamin Dormieu1, Quentin Berlingard3,4, Mickael Casse3 and Philippe Galy1

Noise modeling using look-up tables and DC measurements for cryogenic applications.

VLSI-SoC 2023 - 31st IFIP/IEEE International Conference on Very Large Scale Integration,

Oct 2023, Sharjah, United Arab Emirates.

DOI: 10.1109/VLSI-SoC57769.2023.10321896

hal-04305746

hal-04305746

1STMicroelectronics, Crolles, France

2Univ. Grenoble Alpes, CNRS, Grenoble-INP, TIMA

3Univ. Grenoble Alpes, CEA, LETI

4Univ. Grenoble Alpes, CNRS, Grenoble-INP, IMEP-LAHC

Abstract

: There is today a lack of mature transistor-level compact models for the simulation of integrated circuits at cryogenic temperatures. This is particularly the case for the simulation of the noise behavior which is critical for most applications. In this paper, we aim at an efficient prediction of the white noise behavior of basic amplifying stages working at RF frequencies and cryogenic temperatures. For this, we propose the use of DC measurements that are incorporated in a LookUp Table (LUT) and fed to a mathematical noise model. We illustrate the approach for the case of a transistor in common source configuration. The results of circuit simulation of the noise parameters in the standard temperature range are very close to the estimation of the same parameters using the LUT with just DC measurements. The approach can be readily extended to the analysis of circuits with multiple components. Next, the LUT approach is used for estimating the noise parameters at cryogenic conditions, considering DC measurements that have been carried out at these temperatures. The paper illustrates the feasibility of carrying out a cryogenic design using a LUT-based approach while accurate compact models are not yet available.

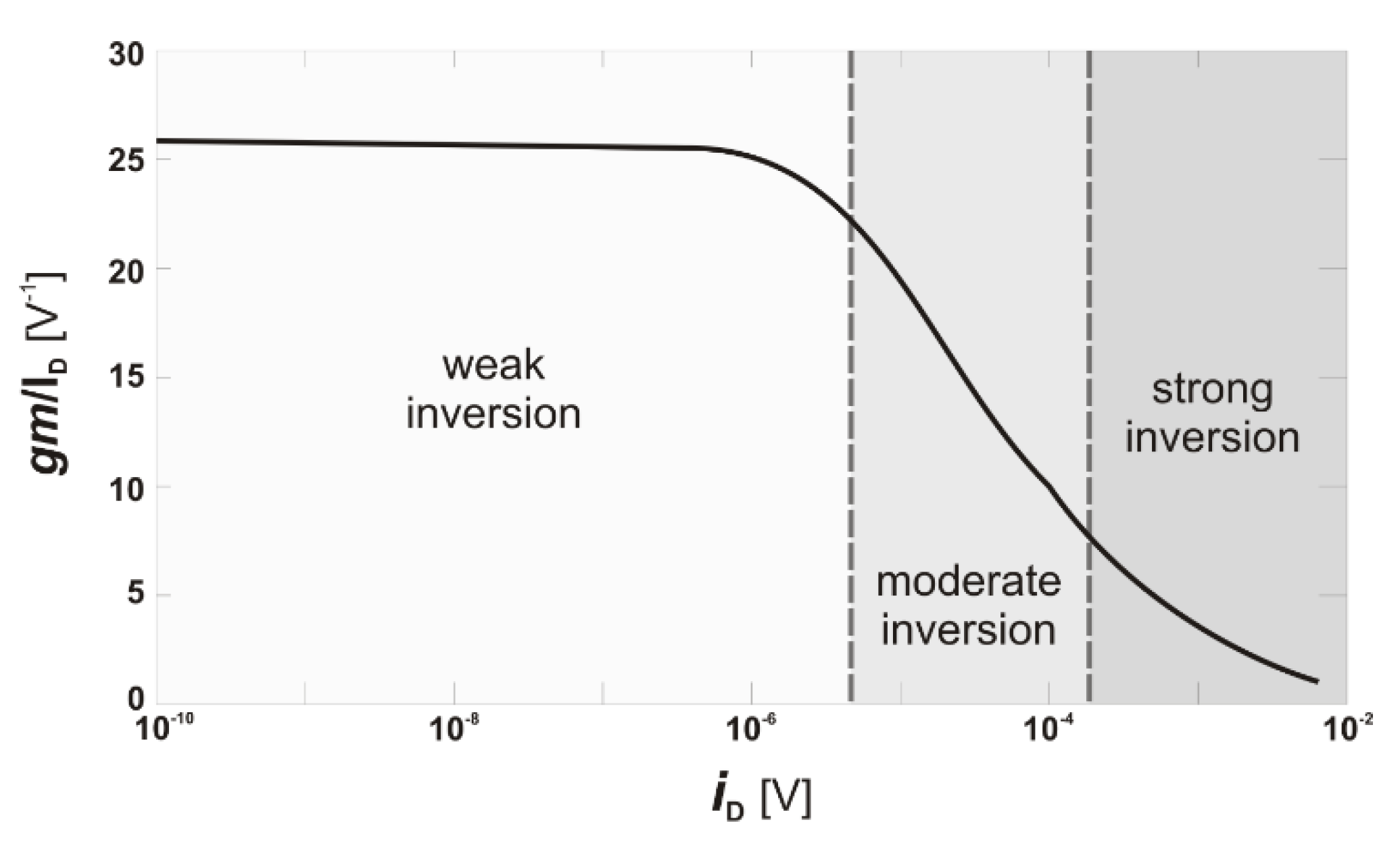

Fig

: Measurement data and EKV or ACM generated parameters are added

to the LUT generated by the interface between EDA tools

Acknowledgments

: This work was supported by the French program Conventions Industrielles de Formation par la Recherche (CIFRE) and Labex MINOS of French program ANR-10-LABX-55-01.