Debnath, P., Sarkar, B., & Chanda, M. (Eds.). (2023).

Differential Equation Based Solutions

for Emerging Real-Time Problems

(1st ed.). CRC Press

DOI 10.1201/9781003227847

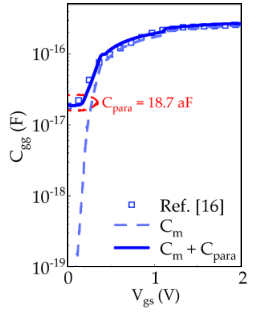

Chapter: Differential Equation-Based Compact 2-D Modeling of Asymmetric Gate Oxide Heterojunction Tunnel FET; By: Sudipta Ghosh, Arghyadeep Sarkar

Abstract: Tunnel Field Effect Transistor (TFET) has emerged as an effective alternative device to replace MOSFET for a few decades. The major drawbacks of MOSFET devices are the short-channel effects, due to which the leakage current increases with a decrease in device dimension. So, scaling down TFET is more efficacious than that of MOSFETs. Sub-threshold swing (SS) is another advantageous characteristic of TFET devices for high-speed digital applications. In TFETs the SS could be well below 60 mV/decade, which is the thermal limit for MOSFET devices and therefore makes it more suitable than MOSFET for faster switching applications. It is observed from the literature studies that the performances of the TFET devices have been explored thoroughly by using 2-D TCAD simulation but an analytical model is always essential to understand the physical behavior of the device and the physics behind this; which facilitates further, the analysis of the device performances at circuit level as and when implemented.Chapter: Differential Equation-Based Analytical Modeling of the Characteristics Parameters of the Junctionless MOSFET-Based Label-Free Biosensors; by: Manash Chanda, Papiya Debnath, Avtar Singh

Abstract: Recently Field Effect transistor (FET)-based biosensing applications have gained significant attention due to the demand for quick and accurate diagnosis of different enzymes, proteins, DNA, viruses, etc; cost-effective fabrication process; portability and better sensitivity and selectivity compared to the existing biosensors. FET is basically a three-terminal device with source, drain, and gate terminals. Basically, the gate terminal controls the current flow between the source and drain terminals. In FETs, first, a nanogap is created in the oxide layer or in the gate by etching adequate materials. When the biomolecules are trapped inside the nanocavity then the surface potentials change and also the threshold voltage varies. As a result, the output current also changes. Finally, by measuring the changes in the threshold voltage or the device current, one can easily detect the biomolecules easily.