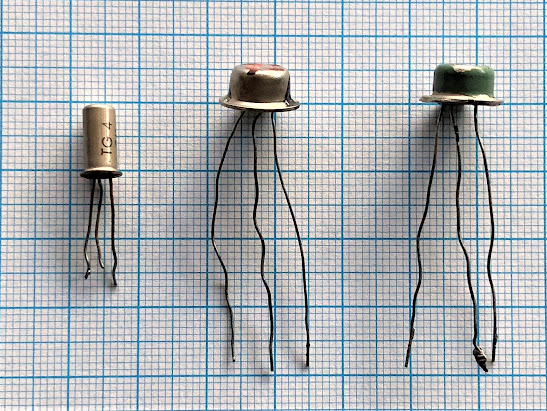

The TG1-TG5 series transistor are the first industrially mass-produced BJT transistors in Poland. The serial production was started by the TEWA Semiconductor Factory, Warsaw, in early1960s. Then, the TG50-TG55 series, was also manufactured by the TEWA in 1961–1962.

The TG4 (see Pic: below) is low power, low frequency, pnp germanium (Ge) alloy transistor (with 75 mW max collector power) [1].

The TG50 (below) is medium power, low frequency, pnp germanium (Ge) alloy transistor (with 175 mW max collector power) [2].

An initial stage of Polish semiconductor microelectronics research activities has been reviewed by Prof. Jerzy Pułtorak. In his paper [3], he has reviewed activities of leading Polish R&D groups starting from Department of Electronics, Polish Academy of Sciences (PAN) founded on July 4, 1952 till foundation of the Instytut Technologii Elektronowej (ITE, Warsaw) early 1960 (now Sieć Badawcza Łukasiewicz - Instytut Mikroelektroniki i Fotoniki). The first, in Poland, experimental germanium point-contact transistor TP-1 [4] has been developed by Prof. Rosinski just after John Bardeen, Walter Brattain and William Shockley have invented a semi-conductor triode (transistor) [5] on December 23, 1947.

Pic: TG4 and two TG50 by the TEWA Semiconductor Factory, Warsaw (PL)

References: [1] TG1-5 / PL Wikipedia/ https://pl.wikipedia.org/wiki/TG1-5

[2] TG50-5 / PL Wikipedia/ https://pl.wikipedia.org/wiki/TG50-55

[3] J. Pułtorak, "60 years of polish transistors," 2014 Proceedings of the 21st International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Lublin, Poland, 2014, pp. 15-21, doi: 10.1109/MIXDES.2014.6872144.

[4] W.Rosinski, J.Groszkowski, “Doswiadczalne tranzystory punktowe model TP” (“Experimental point-cotact transistors model TP”), Arch. Elektrot. 4, 1955, p. 381

[5] J.Bardeen, H.W.Brattain, “The transistor, a semi-conductor triode”, Phys.Rev.74, 7, 1954, p.230

Add Event to Calendar

Add Event to Calendar