Ananda Sankar Chakraborty

Efficient Long-Channel MOSFET Model

with SPICE-enabled Lambert W Function for Universal Application

Silicon (2025): 1-10; DOI 0.1007/s12633-025-03576-1

1 ETCE, Indian Institute of Engineering Science and Technology, Shibpur (IN)

Abstract: A novel, accurate charge-based MOSFET long-channel computational model is presented, which is portable and can be used across the electrical engineering domains ranging from sensing to power electronics, both under sub-threshold as well as super-threshold regime of MOSFET operation. The proposed physics-based model can be universally used to any long-channel MOS-transistor, as it does not depend on any empirical factor and features extremely good computational efficiency. The model uses a novel two-step charge linearization, resulting into accurate drain current and charge model – valid for both the subthreshold and super-threshold regime of long-channel MOSFET operation. Another salient feature of the proposed model is a novel SPICE-compatible numerical solution strategy for the principal branch of the Lambert W function (W0(x) for {x ∈ R | x ≥ 0}). The algorithm is faster than present industry standard implementations, computationally efficient, accurate with maximum percentage error≈10−14% and therefore may be incorporated in a SPICE engine for electrical design and optimization. The proposed computationally efficient long channel MOSFET model is validated against thorough TCAD simulations upto the fourth derivative and has been found to have fast convergence along with much higher degree of accuracy compared to existing MOSFET models.

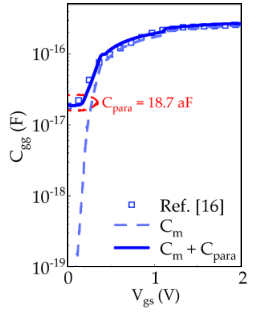

FIG: Bulk-MOSFET structure: its current (IDS) and conductance (gDS) vs Drain Voltage (VDS)

(Line: proposed model, symbol: TCAD)