Sheikh Aamir Ahsan, Member, IEEE, Shivendra Kumar Singh, Chandan Yadav, Member, IEEE, Enrique G. Marín, Member, IEEE, Alexander Kloes, Senior Member, IEEE

and Mike Schwarz, Senior Member, IEEE

A Comprehensive Physics-Based Current–Voltage SPICE Compact Model

for 2-D-Material-Based Top-Contact Bottom-Gated Schottky-Barrier FETs

IEEE Transactions on Electron Devices, vol. 67, no. 11, pp. 5188-5195, Nov. 2020

DOI: 10.1109/TED.2020.3020900

Abstract: In this article, we report the development of a novel physics-based analytical model for explaining the current–voltage relationship in Schottky barrier (SB) 2D material field effect transistors (FETs). The model has at its core the calculation of the surface-potential (SP) which is accomplished by invoking 2-D density of states in conjunction with Fermi–Dirac (FD) distribution for electron and hole statistics. The explicit computation for the SP, carried out using the Lambert-W function together with Halley’s method, is used to construct the SP-based band-diagram for realizing the transparency of the SBs. Thereafter, the ambipolar current is derived in terms of the electron and hole injection phenomena the thermionic emission and Fowler–Nordheim tunneling mechanisms at the SB contacts. Furthermore, drift-diffusion current is derived in terms of the SP and incorporated in the model to account for the scattering in the intrinsic 2D channel. Finally, the Verilog-A model is validated against experimental IV data reported in the literature for two different 2D material systems. This is the first demonstration of an explicit SP-based SPICE model for ambipolar SB-2-D-FETs that is simultaneously built on tunneling-emission and driftdiffusion formalisms.

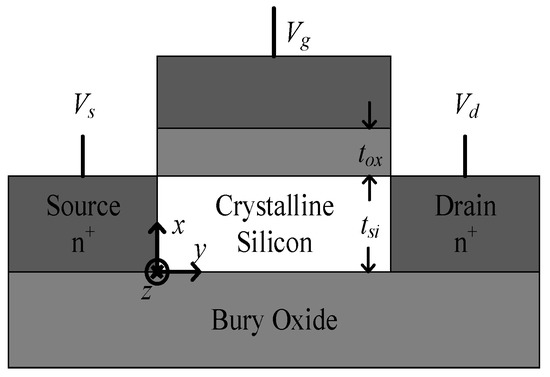

Fig: (a) Band-diagram sketched along positive y-direction underneath the source electrode. Blue and black lines represent bands before and after applying Vgs. (b) ψ-based diagram sketched along positive x, constructed after calculating ψs and ψd. The geometrical screening length λ is given by λ ≈ (tox t2D)^1/2.

Acknowledgement: This work was supported in part by the National Project Implementation Unit (NPIU) through the third phase of Technical Education Quality Improvement Programme (TEQIP-III) Project and in part by DST-SERB Startup Research Grant under Award SRG/2019/001122.