B.Parvais1, R. ElKashlan1, H. Yu, A. Sibaja-Hernandez, B. Vermeersch, V. Putcha, P. Cardinael2, R. Rodriguez, A. Khaled, A. Alian, U. Peralagu, M. Zhao, S.Yadav, G. Gramegna, J. Van Driessche, N. Collaert

Transistor Modelling for mm-Wave Technology Pathfinding

SISPAD, 2021

DOI: 10.1109/SISPAD54002.2021.959253

* imec, Kapeldreef 75, 3001 Leuven, Belgium

1 also with Vrije Universiteit Brussels, 1050 Brussels, Belgium

2 also with UCLouvain, Louvain-la-Neuve, Belgium

Abstract: A review of the modelling requirements to establish a Design-Technology Co-Optimization loop for mmWave Front-End Modules is presented. The example of GaN/Si technology is detailed, and recent modeling developments are explained.

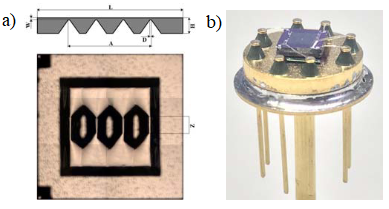

Fig: The RF-DTCO loop concept: from device modeling

and exploration to benchmark circuits.