243rd ECS Meeting – Boston, May 28 – June 2, 2023

"H02 - Advanced CMOS-Compatible Semiconductor Devices 20"

Abstract Submission Deadline (750 words = 1 page): December 1, 2022

You can also use a single "Image Upload" to include Image, figures, equations, tables if necessary.

Abstract submission: https://ecs.confex.com/ecs/243/cfp.cgi

Do not forget to select H02 symposium for submission…

Full text manuscript: The authors of accepted abstracts should submit the full text manuscript for the ECS Transactions no later than March 16, 2023.

This symposium focuses on studies of new devices, circuits and applications for Moore and More-than-Moore technology, including:

I. More-Moore technology contributing to the semiconductor industry

(a) CMOS compatible devices, circuits and applications:

· SOI devices, advanced Bulk MOSFETs, scaled devices and simulations;

· Multi-gate devices (FinFET, triple gate, nanowire, nanosheet), Junctionless FET;

· high-power devices, semiconductor sensors, Tunnel-FET devices, memory devices;

(b) Device physics and process technology using new materials for noise issues of devices and circuits;

(c) Space applications including low-temperature electronics and radiation hardness

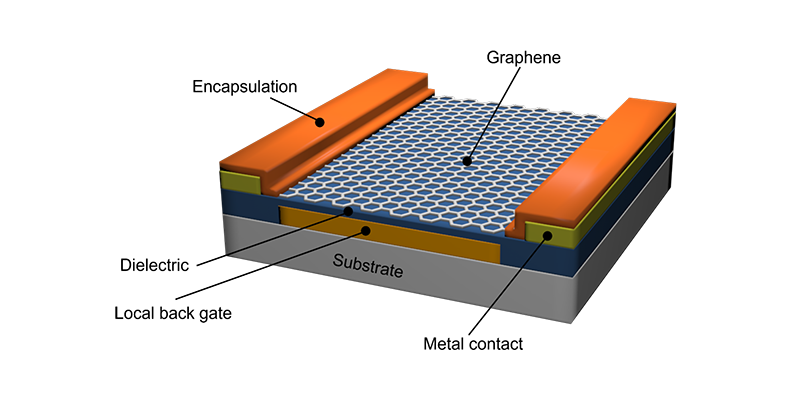

(d) CMOS co-integration of 2D materials (TMDs, etc.)

(e) Self-heating and reliability of scaled MOSFET

(f) Devices with high mobility materials, advanced gate stack

II. More-than-Moore technology

(a) New MEMS applications

(b) Carbon-nanotube and 2D device applications

(c) Sensing applications: Health, environment and security.

(d) Advanced packaging

(e) 2.5D/3D stacking integration

(f) Advanced material and device for Memory, Analog/RF and HV applications

Symposium Organizers:

*Joao Martino (Lead organizer), University of Sao Paulo, Brazil, email: martino@usp.br

*Jean-Pierre Raskin, Universite Catholique de Louvain, Belgium, email: jean-pierre.raskin@uclouvain.be

*Siegfried Selberherr, TU Wien, Austria, email: Selberherr@TUWien.ac.at

*Hiromu Ishii, Toyohashi University of Technology, Japan, email: ishii@ee.tut.ac.jp

*Francisco Gamiz, Universidad de Granada, Spain, email: fgamiz@ugr.es

*Bich-Yen Nguyen, Soitec, USA, email: Bich-yen.Nguyen@soitec.com

*Eddy Simoen, Imec, Belgium, email: eddy.simoen@ugent.be

----------------------------------------

Confirmed INVITED SPEAKERS in alphabetic order by first name:

[1] Dra Bernardette Kunert (Imec, Belgium)

"III-V on Si technologies for 6G electronics"

[2] Prof. Bogdan Cretu (Ensicaen, Caen, France)

"In-deep DC and low frequency noise characterization of double nanosheet FETs DC at room and cryogenic temperatures"

[3] Prof. Cor Claeys (KU Leuven, Leuven, Belgium) – Keynote Speaker

"Technological Challenges and Emerging Device Architectures for Future Semiconductor Micro and Nanoelectronics"

[4] Profa. Cristell Maneux (University of Bordeaux, France)

"RF and mmW technologies"

[5] Prof. Jose Alexandre Diniz (UNICAMP, Brazil)

"ISFET-based Sensors"

[6] Dr. Koen Martens (Imec, Belgium)

"Development of BioFETs based on SOI FinFETs"

[7] Prof. Mathieu Luisier (ETH Zurich, Swiss)

"Modeling of nanoscale devices"

[8] Prof. Prof. Max Fischetti (University of Texas at Dallas, USA)

"The future of nanoelectronics devices s from a theoretical point of view"

[9] Dr. Mikael Cassé (CEA-Leti, France)

"Cryo FD SOI for quantum computing"

[10] Dr. Rüdiger Quay (Fraunhofer Institute for Applied Solid State Physics, Germany)

"Sensor-technology concept and its resource-efficient realization"

[11] Prof. Salvador Gimenez (FEI University Center, Brazil)

"New Layout Styles to Boost the Electrical, Energy, and Frequency Response Performances of Analog MOSFETs"

[12] Dr. Theresia Knobloch (Institue for Microelectronics, TU Wien)

"High-Performance Field Effect Transistors Based on Two-Dimensional Materials"

[13] Prof. Toshihiko Noda (Toyohashi University of Technology, Japan)

"CMOS based multimodal sensing"

[14] Prof. Vihar Georgiev (University of Glasgow, Scotland)

"ISFET for Nano-Biosensing Application"

[15] Prof. Yasuhisa Omura (Kansai University, Japan)

"Potential of Silicon Oxide Films on Low-Cost and High-performance Resistive Switching Devices"