Mar 28, 2024

[paper] Characteristics and ultra-high total ionizing dose response

[paper] Chip Placement with Deep Learning

Abstract: In this work, we present a learning-based approach to chip placement, one of the most complex and time-consuming stages of the chip design process. Unlike prior methods, our approach has the ability to learn from past experience and improve over time. In particular, as we train over a greater number of chip blocks, our method becomes better at rapidly generating optimized placements for previously unseen chip blocks. To achieve these results, we pose placement as a Reinforcement Learning (RL) problem and train an agent to place the nodes of a chip netlist onto a chip canvas. To enable our RL policy to generalize to unseen blocks, we ground representation learning in the supervised task of predicting placement quality. By designing a neural architecture that can accurately predict reward across a wide variety of netlists and their placements, we are able to generate rich feature embeddings of the input netlists. We then use this architecture as the encoder of our policy and value networks to enable transfer learning. Our objective is to minimize PPA (power, performance, and area), and we show that, in under 6 hours, our method can generate placements that are superhuman or comparable on modern accelerator netlists, whereas existing baselines require human experts in the loop and take several weeks.

Mar 26, 2024

[book] NANOELEKTRONIK Bauelemente der Zukunft

NANOELEKTRONIK

| Chapter | Pages |

|---|---|

| Nanoelektronik | 1–13 |

| 1 Einführung in die Nanoelektronik | 15–18 |

| 2 Eigenschaften von Halbleitern | 19–38 |

| 3 Teilchen und Wellen | 39–64 |

| 4 Bandstruktur und Bändermodell | 65–104 |

| 5 Ladungstransport in Halbleitern | 105–124 |

| 6 Grundlagen der Halbleitertechnologie | 125–146 |

| 7 Klassische Bauelemente der Mikroelektronik | 147–222 |

| 8 Digitale CMOS-Schaltungstechnik | 223–242 |

| 9 Nanostruktur-Feldeffekttransistoren | 243–302 |

| 10 Alternative Nanostruktur-MOSFETs | 303–334 |

| Konstanten und Materialparameter | 335–336 |

| Simulationstools | 337–344 |

| Formelzeichen | 345–350 |

| Literatur | 351–354 |

| Index | 355–362 |

Mar 25, 2024

[OSDA 2024] 4th Workshop on Open-Source Design Automation

Welcome Session

ESP: An Open-Source Platform for Collaborative Design of Heterogeneous Systems-on-Chip

Update on the Coriolis EDA Toolchain

FABulous: An embedded eFPGA Framework - an Update

Demo Pitch: Tiny Tapeout

Yosys

Surfer -- An Extensible and Snappy Waveform Viewer

- Vojtech Mrazek

An Open-Source Automated Design Space Exploration Framework for Approximate Accelerators in FPGAs and ASICs - Marc Solé i Bonet, Aridane Alvarez Suarez and Leonidas Kosmidis

The METASAT Hardware Platform v1.1: Identifying the Challenges for its RISC-V CPU and GPU Update - Louis Ledoux and Marc Casas

The Grafted Superset Approach: Bridging Python to Silicon with Asynchronous Compilation and Beyond - Manfred Schlägl, Christoph Hazott and Daniel Große

RISC-V VP++: Next Generation Open-Source Virtual Prototype - Guillem López-Paradís, Brian Li, Adrià Armejach, Stefan Wallentowitz, Miquel Moretó and Jonathan Balkind

Using Supercomputers to Parallelize RTL Simulations - Davide Cieri

Hog (HDL on git): a tool to manage HDL code on a git repository - Jakob Ratschenberger and Harald Pretl

RALF: A Reinforcement Learning Assisted Automated Analog Layout Design Flow - Ajeetha Kumari Venkatesan, Anirudh Pradyumnan Srinivasan, Deepa Palaniappan

Adding configurability to PySlint using TOML - Lucas Klemmer and Daniel Grosse

WSVA: A SystemVerilog Assertion to WAL Compiler

Mar 21, 2024

[FOSSEE] Better Education

- Scilab

free/libre and open source software for numerical computation developed by Scilab Enterprises, France. Scilab also includes Xcos which is an open source alternative to Simulink. - Python

general-purpose, high-level, remarkably powerful dynamic programming language that is used in a wide variety of application domains. It supports multiple programming paradigms. - eSim

(formerly known as Oscad/FreeEDA) is an EDA tool for circuit design, simulation, analysis and PCB design. It is developed by the FOSSEE team at IIT Bombay - Osdag

free/libre and open-source software which allows the user to design steel structures using a graphical user interface. The GUI also provides 3D visualization of the designed component and images - DWSIM

free/libre and open source CAPE-OPEN compliant chemical process simulator. Helps understand the behavior of Chemical Systems by using rigorous thermodynamic and unit operations models. - OpenFOAM

free/libre and open source CFD toolbox useful to solve anything from complex fluid flows involving chemical reactions, turbulence and heat transfer, to solid dynamics and electromagnetics. - OpenModelica

free/libre and open source environment based on the Modelica modelling language for modelling, simulating, optimising and analysing complex dynamic systems. - OpenPLC

free/libre and open source Programmable Logic Controller creating opportunities for people to study its concepts, explore new technologies and share the resources. - FLOSS-Arduino

control of Arduino using Free/Libre Open-Source Software. The interface helps the user to perform embedded systems experiments on the Arduino Uno board. - SBHS

(Single Board Heater System) is a lab-in-a-box setup useful for teaching and learning control systems. - R

programing language and environment for statistical computing and graphics. - QGIS

(Quantum GIS) is a free and open-source desktop Geographic Information System (GIS) application. - FOCAL

an initiative by FOSSEE to promote Open Source Software in computer graphics. - SOUL

(Science OpensoUrce Software for Teaching Learning) is a collection of ICT software that can be used as teaching/learning tools by the community of educators and the learners to teach/ learn the basic as well as the advanced concepts in science subjects

Mar 20, 2024

[gnugen] Install Fest and Workshop git

Come discover Linux and if you want, we'll be ready to help you install it on your computer !

(remember to take a backup of your data before, just in case)

📌 Where: EPFL CM 1 100

Workshop: just do git, at 13h30 if you'd like to learn how to use git for an efficient collaboration

Mar 19, 2024

[Habilitation] Assessment of novel devices in CMOS technology

IEEE 5NANO2024 Conference 25-26th April, 2024

Nanomaterials, Nanobioscience & Nanotechnology

VISAT Engineering College,

Elanji, Ernakulam, Kerala, India - 686 665

Tel: +91 9447691397, +91 9486881397.

E-mail: deanresearch@visat.ac.in, tdsubash2007@gmail.com, 5nano2k24@gmail.com

Website: https://www.5nano2024.com

Mar 18, 2024

[paper] in-memory computing using FeFET

1 Robert Bosch GmbH, Renningen, Germany

2 Semiconducture Test and Reliability, University of Stuttgart, Stuttgart, Germany

3 Department of Electrical Engineering, IIK, Kanpur, India

4 Fraunhofer IPMS, Dresden, Germany

5 RPTU Kaiserslautern-Landau, Kaiserslautern, Germany

6 MIRMI; Technical University of Munich, Germany

Abstract: Advancements in AI led to the emergence of in-memory-computing architectures as a promising solution for the associated computing and memory challenges. This study introduces a novel in-memory-computing (IMC) crossbar macro utilizing a multi-level ferroelectric field-effect transistor (FeFET) cell for multi-bit multiply and accumulate (MAC) operations. The proposed 1FeFET-1R cell design stores multi-bit information while minimizing device variability effects on accuracy. Experimental validation was performed using 28 nm HKMG technology-based FeFET devices. Unlike traditional resistive memory-based analog computing, our approach leverages the electrical characteristics of stored data within the memory cell to derive MAC operation results encoded in activation time and accumulated current. Remarkably, our design achieves 96.6% accuracy for handwriting recognition and 91.5% accuracy for image classification without extra training. Furthermore, it demonstrates exceptional performance, achieving 885.4 TOPS/W–nearly double that of existing designs. This study represents the first successful implementation of an in-memory macro using a multi-state FeFET cell for complete MAC operations, preserving crossbar density without additional structural overhead.

Acknowledgements: This work has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No 826655 and No 876925. The JU receives support from the European Union’s Horizon 2020 research and innovation programme and Belgium, France, Germany, Portugal, Spain, The Netherlands, Switzerland. Open Access funding enabled and organized by Projekt DEAL.

[paper] Symmetric BSIM-SOI

Mar 17, 2024

SSCS April Technical Webinar

- https://zerotoasiccourse.com/

- https://tinytapeout.com

Mar 15, 2024

[paper] Topological Transistor Compact Model

1 Department of Electrical Engineering and Computer Science, The University of Tennessee, USA

2 Department of Physics, Princeton University, USA

[paper] Next Wave for AI/ML in Physical Design

Mar 11, 2024

Importance of Open-Source EDA Tools for Academia

Luca Benini

University of Bologna, Italy & ETH Zürich, Switzerland

Professor, Lead of the RISC-V PULP platform

Giovanni De Micheli

EPFL Lausanne, Switzerland

Professor and Director, LSI lab

Marie-Minerve Louërat

Sorbonne University, France

Research Scientist, Coriolis Foundation hosted by CNRS Foundation

Harald Pretl

Johannes Kepler University Linz, Austria

Professor, Maintainer of IIC-OSIC-TOOLS

Stefan Wallentowitz

Hochschule München University of Applied Sciences, Germany

Professor, Director at FOSSi Foundation & Director at RISC-V

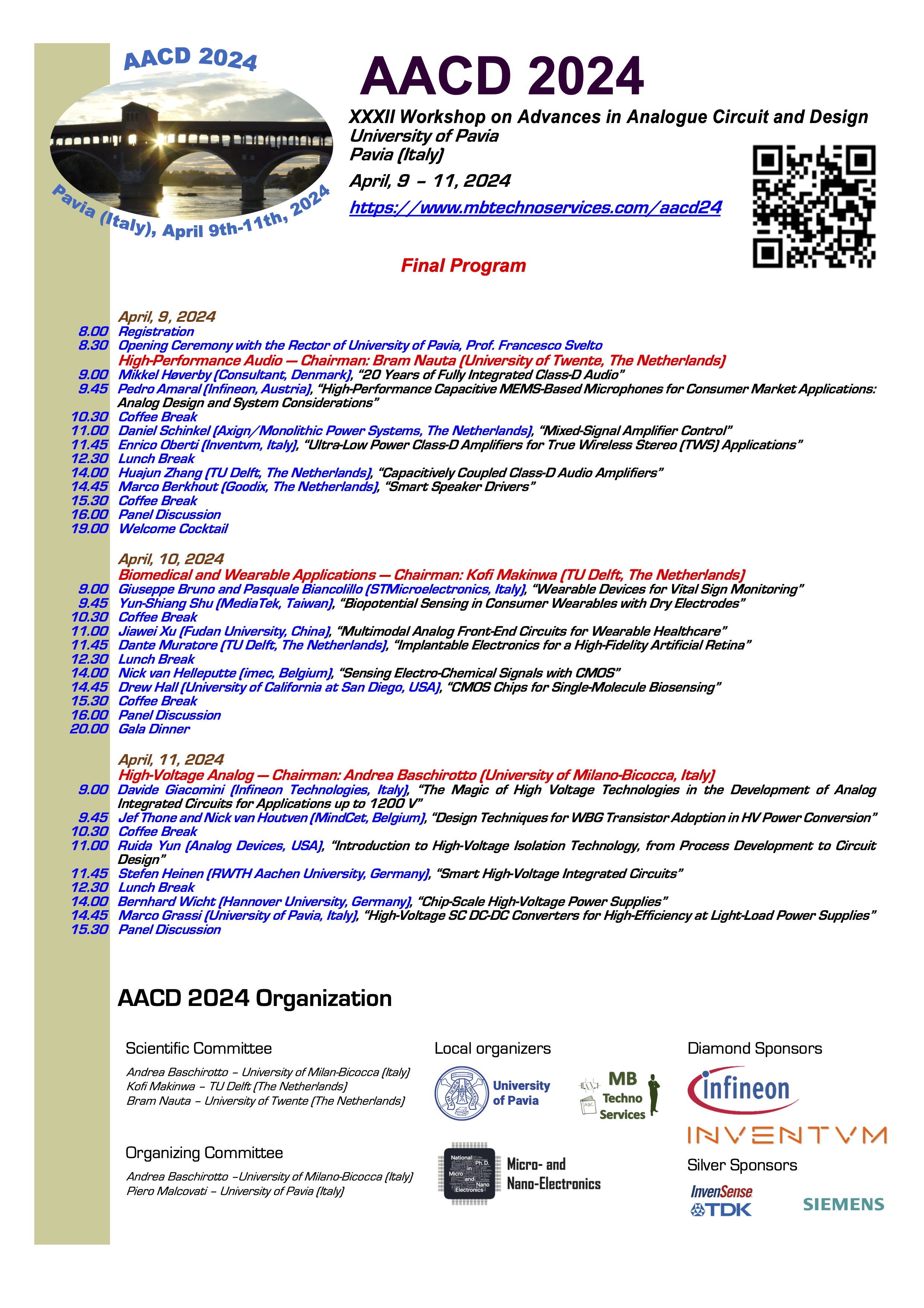

AACD 2024 Final Program

Registration to AACD24 is open at:

https://www.mbtechnoservices.com/aacd24/index.php?page=Registration.html

For any further information:

- Visit http://www.mbtechnoservices.com/aacd24

- Contact the AACD24 Organizing Committee: Andrea Baschirotto (andrea.baschirotto@unimib.it), Piero Malcovati (piero.malcovati@unipv.it)

We look forward to meeting you in Pavia for this very exciting edition of the AACD Workshop!!!!

Andrea Baschirotto

Piero Malcovati AACD24 Organizing Committee

Mar 5, 2024

[Open PDK] IEEE EDS DL at IISc Banglare

| DATE AND TIME | LOCATION | HOSTS |

|---|---|---|

|

Date: 07 Mar 2024

Time: 04:00 PM to 05:00 PM All times are (UTC+05:30) Chennai Add Event to Calendar iCal Google Calendar |

Auditorium, Dept. of ESE,

IISc Bangalore Karnataka India 560012 |

Bangalore Section

Jt. Chapter ED15/SSC37 |

Mar 4, 2024

[EDTM] Open PDK Initiative

The EDTM Conference to host two contributions discussing the status of Open PDK Initiative:

[6C-1] [Invited] Disrupting Conventional Chip Design through the Open Source EDA Ecosystem

Mehdi Saligane; University of Michigan, USA

[P2-36] FOSS CAD for the Compact Verilog-A Model Standardization in Open PDKs

Wladek Grabinski, et al. MOS-AK (EU); IHP - Leibniz-Insitut für innovative Mikroelektronik;

[EDTM] Inauguration Session

The 8th Electron Devices Technology and Manufacturing Conference (IEEE EDTM 2024) will be held for the first time in India at Bangalore; the Silicon Valley of India and the hub of semiconductor companies. IEEE EDTM 2024 will be a full four-day conference to be held during March 3-6, 2024. IEEE EDTM 2024 aims to be a premier global forum for researchers and engineers from around the world coming to share new discoveries and discuss any device/manufacturing-related topics, including but not limited to, materials, processes, devices, packaging, modeling, reliability, manufacturing and yield, tools, testing, and any emerging device technologies, as well as workforce training.

Plenary Talk by Prof. Chenming Hu "Semiconductor – the Next 75 Years?"