(b) the RCSJ model of a Josephson junction.

Jun 30, 2020

[paper] Compact Model for SIS Josephson Junctions

(b) the RCSJ model of a Josephson junction.

[paper] 3D Vertical JL GAA Si Nanowire Transistors

Chhandak Mukherjee1, Guilhem Larrieu2 and Cristell Maneuxsup1

Compact Modeling of 3D Vertical Junctionless Gate-all-around Silicon Nanowire Transistors

EuroSOI-ULIS 2020, Sep 2020, Caen (F)

1IMS Laboratory, University of Bordeaux, France

2LAAS-CNRS, Université de Toulouse, France

HAL: hal.archives-ouvertes.fr/hal-02869216

Abstract: This paper presents a physics based, computationally efficient compact modeling approach for 3D vertical gate-all-around junctionless nanowire transistor (JLNT) arrays designed for future high performance computational logic circuit. The model features an explicit continuous analytical form adapted for a 14 nm channel JLNT technology and has been validated against extensive characterization results on a wide range of JLNT geometry, depicting good accuracy. Finally, preliminary logic circuit simulations have been performed for benchmarking performances of transistor logic circuits, such as inverters and ring oscillators, designed using the developed model.

Fig: The vertical JLNT: (a) SEM image of nanowire arrays,

(b) single nanowire showing its (c) gate formation

Acknowledgement: This work is supported by ANR under Grant ANR-18- CE24-0005-01

[webinar] Differentiated FDSOI for mmWave Solutions

More information at the IEEE EDS Santa Clara Valley-San Francisco Chapter Home Page

Subscribe or Invite your friends to sign up for our mailing list and get to hear about exciting electron-device relevant talks. We promise no spam and try to minimize email. You can unsubscribe easily.

Jun 29, 2020

IEEE SSCS-EDS Distinguished Talks (Webinar) Systematic Design of Analog CMOS Circuits Dr. Paul Jespers, UCLouvain, Louvain-la-Neuve, Belgium July 09th, 13h30 (Brasilia Time, GMT-3) https://t.co/d3HL96l2xT https://t.co/FQOFMq4FJG #paper https://t.co/zelqSxMxGI

IEEE SSCS-EDS Distinguished Talks (Webinar)

— Wladek Grabinski (@wladek60) June 29, 2020

Systematic Design of Analog CMOS Circuits

Dr. Paul Jespers, UCLouvain, Louvain-la-Neuve, Belgium

July 09th, 13h30 (Brasilia Time, GMT-3)https://t.co/d3HL96l2xT https://t.co/FQOFMq4FJG#paper pic.twitter.com/zelqSxMxGI

from Twitter https://twitter.com/wladek60

June 29, 2020 at 11:04AM

via IFTTT

Jun 26, 2020

Creating A Custom ASIC With The First Open Source PDK: The FOSSi foundation now reports on a new, open PDK project launched by Google and SkyWater Technology https://t.co/6G78tYz4c1 #model https://t.co/NOCZS6YMr5

Creating A Custom ASIC With The First Open Source PDK: The FOSSi foundation now reports on a new, open PDK project launched by Google and SkyWater Technology https://t.co/6G78tYz4c1#model pic.twitter.com/NOCZS6YMr5

— Wladek Grabinski (@wladek60) June 26, 2020

from Twitter https://twitter.com/wladek60

June 26, 2020 at 02:14PM

via IFTTT

Jun 25, 2020

Neurotransistor MatLab Code

Code availability: The MatLab code that supports the mathematical model in this article is available

at https://github.com/eunhye8747/MatLab-Code-Neurotransistor

[paper] Ge Twin-Transistor NVM with FinFET Structure

Abstract: Germanium is a promising alternative material for use in advanced technology nodes because it exhibits symmetrical mobility of holes and electrons. Embedded nonvolatile memory (NVM) is essential in electronic devices with integrated circuit (IC) technology, including future Ge-based technology. In this paper, we demonstrate Ge twin-transistor NVM with a fin field-effect transistor (FinFET) structure. This Ge twin-transistor NVM exhibits high programming and erasing speeds and satisfactory reliability. Moreover, the masks and fabrication process of this Ge twin-transistor NVM are identical to those of Ge-channel FinFETs. Thus, Ge twin-transistor NVM is a promising candidate for embedded NVM applications in future high-performance Ge complementary metal–oxide–semiconductor technology (CMOS).

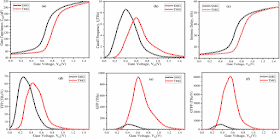

[paper] Statistical modelling of oTFT

Jun 24, 2020

[paper] Hot Carrier Degradation in n-MOSFETs

EEE SSCS-EDS Distinguished Talks (Webinar) Low-power Circuits for IoT Dr. Jorge Fernandes, INESC-ID, Lisbon, Portugal. Next Thursday, June 25th, 2:00 PM (Brasilia Time, GMT-3) https://t.co/wJuF6ryZHW #paper https://t.co/6jrZWrKTAh

EEE SSCS-EDS Distinguished Talks (Webinar)

— Wladek Grabinski (@wladek60) June 24, 2020

Low-power Circuits for IoT

Dr. Jorge Fernandes, INESC-ID, Lisbon, Portugal.

Next Thursday, June 25th, 2:00 PM (Brasilia Time, GMT-3) https://t.co/wJuF6ryZHW#paper pic.twitter.com/6jrZWrKTAh

from Twitter https://twitter.com/wladek60

June 24, 2020 at 02:30PM

via IFTTT

[paper] AlGaN/AlN/GaN/AlGaN photodetector

[paper] Compact Modeling of Parasitic FET capacitance

[paper] SPICE Model for Bipolar Resistive Switching Devices

Jun 23, 2020

Webinar Series by Distinguished Experts

Stay up to date with the latest developments in the MEMS areas with IEEE RightNow. Access for J-MEMS. Enjoy temporary Open Access to selected featured publications https://t.co/mxoRhbT802 #paper https://t.co/9h5EV2mEBf

Stay up to date with the latest developments in the MEMS areas with IEEE RightNow. Access for J-MEMS. Enjoy temporary Open Access to selected featured publicationshttps://t.co/mxoRhbT802#paper pic.twitter.com/9h5EV2mEBf

— Wladek Grabinski (@wladek60) June 23, 2020

from Twitter https://twitter.com/wladek60

June 23, 2020 at 11:56AM

via IFTTT

Jun 22, 2020

[paper] “Extrinsic” Compact Model of the MOSFET Drain Current

[paper] Analog/RF Tri-metal Gate FinFET

[virtual] ToM2020/2 Announcement

14.00-17.30 Danilo Gerna (Melexis Technologies), “Advanced Hall Element Based Magnetic Sensors Front End Design”

September, 9th, 2020

9.00-12.30 Carlo Samori (Milan Politechnic), “PLL: From Analog to Digital and Recent Trends”

14.00-17.30 Alex Tranca (Infineon), “Robust Design of Smart Power ICs for Automotive Applications, with Focus on Load Current Sensing”

September, 10th, 2020

9.00-12.30 Alfio Dario Grasso (Univ. Catania), “Ultra-Low Power Amplifiers for IoT Nodes”

14.00-17.30 Gabriella Ghidini (STMicroelectronics), “Dielectric Reliability in Microelectronics”

In this particular situation, the PhD School at University of Milan-Bicocca decided to fully support the costs of the ToM2020/2 course, whose participation will then be free-of-charge for the attendees. However, for proper managing internet access to the virtual ToM2020/2 course, registration is mandatory at the following website:

http://www.innotechevents.com/index.php?page=ToM/RegistrationForm.html

Only registered participants will receive access information for the course.

At the end of the course, an exam will be proposed for certifying the positive attendance (please register to the exam with the course registration).

We look forward to virtually meeting you !!!!

More information at:

http://www.innotechevents.com/index.php?page=ToM/ToM.html

[virtual] IEEE EDS DL Mini-Colloquium at MIXDES Wroclaw

10.00-10.45

|

Arokia

Nathan "Ultralow Power,

High-Resolution Sensor Interfaces"

EDS

Distinguished Lecturer, Cambridge Touch Technologies, UK; E-mail: an299@cam.ac.uk

|

10.45-11.30

|

Mike

Schwarz "Sensor Design –

From Prototype to Series"

Robert

Bosch GmbH, 72703 Reutlingen,Germany; E-mail: Mike.Schwarz@de.bosch.com

|

12.00-12.45

|

Benjamin

Iñíguez "Compact Modeling and

Parameter Extraction for Oxide and Organic Thin Film Transistors (TFTs) from

150K to 350K"

EDS

Distinguished Lecturer, Department of Electrical, Electronics Engineering and

Automatic Control Engineering, Universitat Rovira i Virgili, 43007 Tarragona,

Spain; E-mail: benjamin.iniguez@urv.cat

|

12.45-13.30

|

Teoder

Gotszalk " Microsystem

Electronics and Photonics "

Faculty

of Microsystem Electronics and Photonics, Wroclaw University of Technology,

Poland; E-mail: teodor.gotszalk@pwr.edu.pl

|

13.30-14.15

|

Mina

Rais-Zadeh "Phase change electro-optical devices for space applications" (recorded)

EDS

Distinguished Lecturer, NASA Jet Propulsion Lab., California Institute of

Techn., USA; E-mail: minar@umich.edu

|

Jun 19, 2020

#SilTerra - #MEMS Technology Roadmap https://t.co/X0g0M0ImoL #paper https://t.co/n0Nthns32a

#SilTerra - #MEMS Technology Roadmap https://t.co/X0g0M0ImoL #paper pic.twitter.com/n0Nthns32a

— Wladek Grabinski (@wladek60) June 19, 2020

from Twitter https://twitter.com/wladek60

June 19, 2020 at 10:29AM

via IFTTT

Jun 18, 2020

[Short Course] Modeling and Simulation of Nano-Transistors

Jun 17, 2020

A Benchmark Study Of Complementary-Field Effect Transistor (#FET) Process Integration Options: Comparing #Bulk vs. #SOI vs. DSOI Starting Substrates https://t.co/rYE24rym7L #paper https://t.co/T3ECdVJa5c

A Benchmark Study Of Complementary-Field Effect Transistor (#FET) Process Integration Options: Comparing #Bulk vs. #SOI vs. DSOI Starting Substrates https://t.co/rYE24rym7L #paper pic.twitter.com/T3ECdVJa5c

— Wladek Grabinski (@wladek60) June 17, 2020

from Twitter https://twitter.com/wladek60

June 17, 2020 at 05:02PM

via IFTTT

[paper] CV of Graphene–Silicon Heterojunction Photodiodes

[paper] Compact Model for Ferroelectric FET

#Samsung #MOSIS Collaboration https://t.co/IOrXK5W1Y8 #paper https://t.co/VXZqf03bmY

#Samsung #MOSIS Collaboration https://t.co/IOrXK5W1Y8 #paper pic.twitter.com/VXZqf03bmY

— Wladek Grabinski (@wladek60) June 17, 2020

from Twitter https://twitter.com/wladek60

June 17, 2020 at 09:14AM

via IFTTT

Jun 16, 2020

Learning with brain chemistry https://t.co/UJRbFdHuUh #paper https://t.co/PB4Ty0moUg

Learning with brain chemistry https://t.co/UJRbFdHuUh #paper pic.twitter.com/PB4Ty0moUg

— Wladek Grabinski (@wladek60) June 16, 2020

from Twitter https://twitter.com/wladek60

June 16, 2020 at 05:39PM

via IFTTT

#GNU #Health #Embedded #OpenSource Health Platform Works on Raspberry Pi 3/4, and soon Olimex SBC's https://t.co/mIXu3NfQPy https://t.co/I0tkTqXijs

#GNU #Health #Embedded #OpenSource Health Platform Works on Raspberry Pi 3/4, and soon Olimex SBC's https://t.co/mIXu3NfQPy pic.twitter.com/I0tkTqXijs

— Wladek Grabinski (@wladek60) June 16, 2020

from Twitter https://twitter.com/wladek60

June 16, 2020 at 04:46PM

via IFTTT

[paper] TFT Compact Modeling

#Intel’s #10nm Node: Past, Present, and Future [EETimes] https://t.co/P3Fi3xUogJ #paper https://t.co/QoFX5z22br

#Intel’s #10nm Node: Past, Present, and Future [EETimes] https://t.co/P3Fi3xUogJ #paper pic.twitter.com/QoFX5z22br

— Wladek Grabinski (@wladek60) June 16, 2020

from Twitter https://twitter.com/wladek60

June 16, 2020 at 02:31PM

via IFTTT

[slides] (Ultra-) Wide-Bandgap Devices

Center for Power Electronics Systems, Virginia Tech

The seminar presentation is now available on our IEEE EDS SCV-SF webpage:

http://site.ieee.org/scv-eds/files/2020/06/SCV_SF_EDS_Yuhao_Zhang_excerpt.pdf

More information at the IEEE EDS Santa Clara Valley-San Francisco Chapter Home Page. Subscribe or Invite your friends to sign up for our mailing list and get to hear about exciting electron-device relevant talks. We, EDS SCV-SF, promise no spam and try to minimize email. You can (un)subscribe easily.

Jun 15, 2020

[paper] Future of Ultra-Low Power SOTB CMOS

2.Renesas Electronics Corp.Tokyo, Japan

3.The University of Tokyo, Japan

IEEE PS Webinar "G2V and V2G Technologies in Electric Vehicles"

- Date:16-06-2020

- Time:10:30 - 11:30 AM IST

- Pre registration link: https://bit.ly/3dTeDzP

- Topic: G2V and V2G Technologies in Electric Vehicles

- Speaker: Dr.Sreejith.S; Assistant Professor,

Department of Electrical Engineering,

National Institute of Technology, Silchar, Assam

We, IEEE Photonics Society Student Chapter, invite you all to join this webinar and take away some useful stuffs in this quarentine. Registration free!!! See you there. All registered participants are honoured with e-certificates

Webinar Link: https://bit.ly/2ZgJuBY

For further queries contact our coordinators:

Alsufiyan : +91 7736598136

Nandhu : +91 9061383258

Stay Safe, Enjoy learning!! Stay updated with us for more exciting events!...